module pulse_gen_en (

input clk ,

input rstb ,

input en_s , // using enable = 1

input en , // enable signal input

input in ,

output out

);

reg in_dly0;

reg in_dly1;

always@(posedge clk or negedge rstb)

if(~rstb) begin

in_dly0 <= 1'b0;

in_dly1 <= 1'b0;

end

else

case(en_s)

0 : begin

in_dly0 <= in;

in_dly1 <= in_dly0;

end

1 : if(en)

in_dly0 <= in;

else

in_dly1 <= in_dly0;

endcase

assign out = in_dly0 & ~in_dly1 ;

endmodule

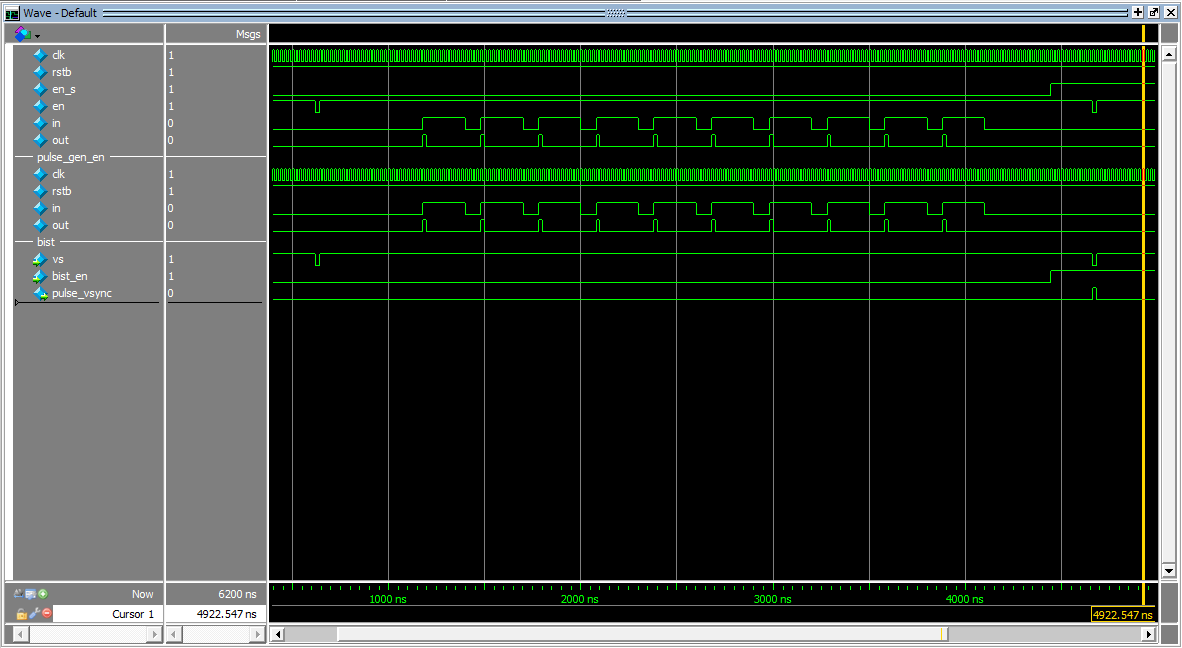

pulse_gen_en u0_pulse_gen_en (

.clk (clk ),

.rstb (rstb ),

.en_s (1'b0 ),

.en ( ),

.in (in ),

.out (out )

);

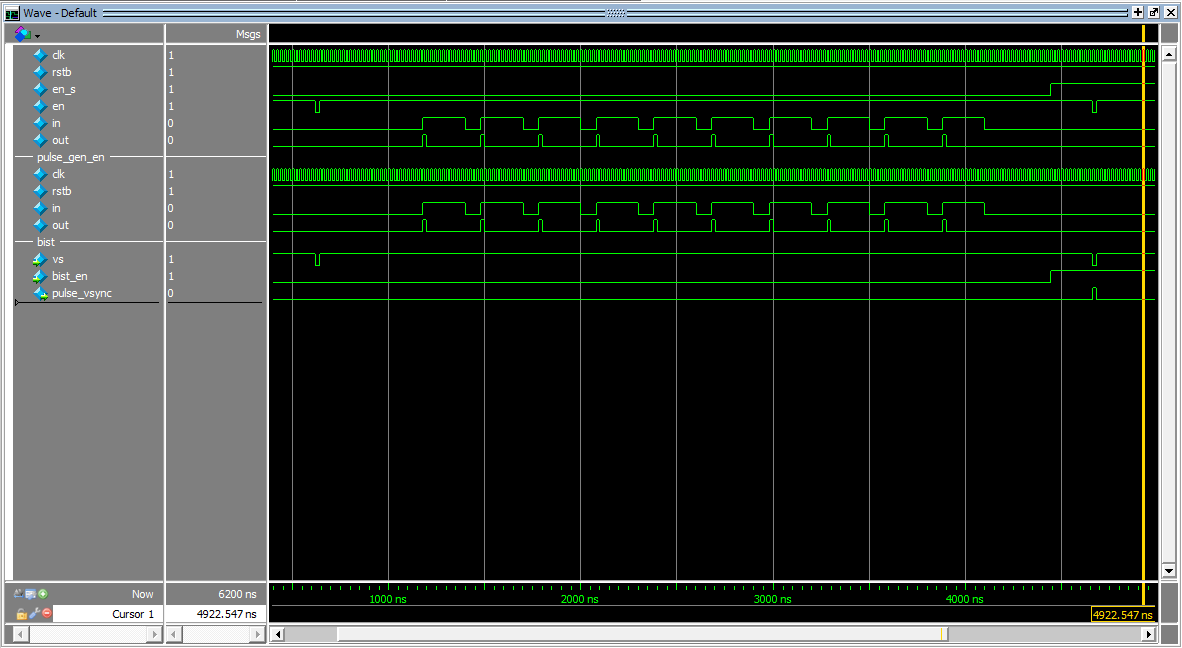

pulse_gen_en pulse_gen_en_u0 (

.clk (clk ),

.rstb (rstb ),

.en_s (1'b1 ),

.en (~vs ),

.in (bist_en ),

.out (pulse_vsync)

);