`include "../lab3_2/seven_segment_cntrl.v"

`include "../simple_uart_rx/simple_uart_rx.v"

module rx_seg(

input clk,

input reset_n,

input rx,

output seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g,

output seg_h, seg_i, seg_j, seg_k, seg_l, seg_m, seg_n

);

wire [7:0] rxtx;

simple_uart_rx uSimple_rx(

.clk(clk),

.reset_n(reset_n),

.rx(rx),

.rx_data(rxtx)

);

seven_segment_cntrl uSeven_segment_cntrl1(

.inp(rxtx[7:4]),

.seg_a(seg_a),

.seg_b(seg_b),

.seg_c(seg_c),

.seg_d(seg_d),

.seg_e(seg_e),

.seg_f(seg_f),

.seg_g(seg_g)

);

seven_segment_cntrl uSeven_segment_cntrl0(

.inp(rxtx[3:0]),

.seg_a(seg_h),

.seg_b(seg_i),

.seg_c(seg_j),

.seg_d(seg_k),

.seg_e(seg_l),

.seg_f(seg_m),

.seg_g(seg_n)

);

endmodule//testbench

`timescale 1 ns / 1 ns

module rx_seg_tb();

reg clk;

reg reset_n;

reg rx;

wire seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g;

wire seg_h, seg_i, seg_j, seg_k, seg_l, seg_m, seg_n;

rx_seg uRx_seg(

.clk(clk),

.reset_n(reset_n),

.rx(rx),

.seg_a(seg_a),

.seg_b(seg_b),

.seg_c(seg_c),

.seg_d(seg_d),

.seg_e(seg_e),

.seg_f(seg_f),

.seg_g(seg_g),

.seg_h(seg_h),

.seg_i(seg_i),

.seg_j(seg_j),

.seg_k(seg_k),

.seg_l(seg_l),

.seg_m(seg_m),

.seg_n(seg_n)

);

initial begin

clk = 1'b1;

forever #10 clk = ~ clk;

end

initial begin

reset_n = 1'b1;

end

initial begin

rx = 1'b1;

#20000 rx = 1'b0;

#4340 rx = 1'b0;

//ASCII 'X'

#8680 rx = 1'b0;

#8680 rx = 1'b0;

#8680 rx = 1'b0;

#8680 rx = 1'b1;

#8680 rx = 1'b1;

#8680 rx = 1'b0;

#8680 rx = 1'b1;

#8680 rx = 1'b0;

//STOP

#8680 rx = 1'b1;

#8680 rx = 1'b1;

#8680 rx = 1'b1;

#8680 rx = 1'b0;

#4340 rx = 1'b0;

//ASCII 'A'

#8680 rx = 1'b1;

#8680 rx = 1'b0;

#8680 rx = 1'b0;

#8680 rx = 1'b0;

#8680 rx = 1'b0;

#8680 rx = 1'b0;

#8680 rx = 1'b1;

#8680 rx = 1'b0;

//STOP

#8680 rx = 1'b1;

#8680 rx = 1'b1;

end

endmodule

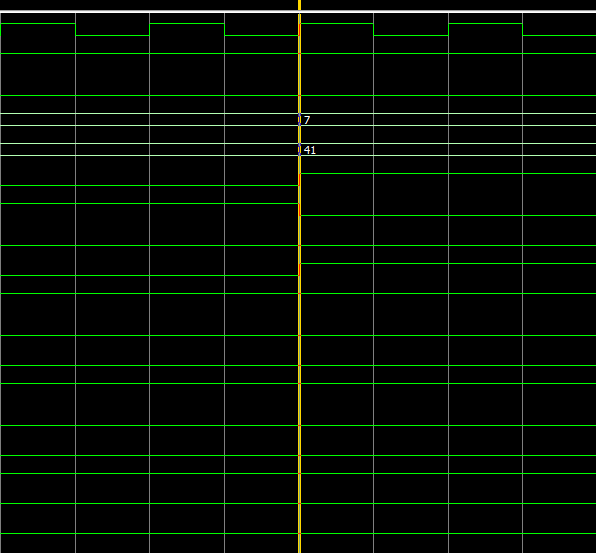

ASCII 'X' : 0x58, 'A' : 0x41

DE1-SoC

ASCII Code : X(0x58), A(0x41), Z(0x5A), reset_n(key0)

// tcl file

vlib work

vlog rx_seg.v rx_seg_tb.v

vsim work.rx_seg_tb

view wave

add wave -radix bin /clk

add wave -radix bin /reset_n

add wave -radix bin /rx

add wave -radix unsigned /uRx_seg/uSimple_rx/cst

add wave -radix hex /uRx_seg/rxtx

add wave -radix bin /seg_a

add wave -radix bin /seg_b

add wave -radix bin /seg_c

add wave -radix bin /seg_d

add wave -radix bin /seg_e

add wave -radix bin /seg_f

add wave -radix bin /seg_g

add wave -radix bin /seg_h

add wave -radix bin /seg_i

add wave -radix bin /seg_j

add wave -radix bin /seg_k

add wave -radix bin /seg_l

add wave -radix bin /seg_m

add wave -radix bin /seg_n

run 232us'[Harman] 반도체 설계 > Quartus' 카테고리의 다른 글

| Quartus II project - Verilog HDL Design pptx. (3) | 2023.08.27 |

|---|---|

| Quartus II project - Uart Rx Segment [2]. (0) | 2023.08.19 |

| Quartus II project - Simple Uart Rx. (0) | 2023.08.16 |

| Quartus II Project - Falling Edge Detection. (0) | 2023.08.15 |

| Quartus II Project - notes [2] (0) | 2023.08.13 |