d_ff 을 통해서 Falling Edge 를 파악하고, Data 송수신의 Start bit 를 확인할 수 있다.

module fdet(

input clk,

input reset_n,

input rx,

output f_det

);

reg rx_reg;

reg rx_delay1;

reg rx_delay2;

always @(posedge clk, negedge reset_n) begin

if(!reset_n) begin

rx_delay1 <= 0;

rx_delay2 <= 0;

end

else begin

rx_reg <= rx;

rx_delay1 <= rx_reg;

rx_delay2 <= rx_delay2;

end

end

assign f_det = rx_delay2 & ~rx_delay1;

endmodule

// test-bench

`timescale 1 ns / 1 ns

module fdet_tb();

reg clk;

reg reset_n;

reg rx;

wire f_det;

fdet uFdet(

.clk(clk),

.reset_n(reset_n),

.rx(rx),

.f_det(f_det)

);

initial begin

clk = 1'b0;

forever #10 clk = ~clk;

end

initial begin

reset_n = 1'b1;

#15 reset_n = 1'b0;

#10 reset_n = 1'b1; //#25

end

initial begin

rx = 1'b1

#90 rx = 1'b0;

end

endmodule// tcl file

vlib work

vlog fdet.v fdet_tb.v

vsim work.fdet_tb

view wave

add wave -radix bin /clk

add wave -radix bin /reset_n

add wave -radix bin /rx

add wave -radix bin /fdet_tb/uFdet/rx_delay1

add wave -radix bin /fdet_tb/uFdet/rx_delay2

add wave -radix bin /f_det

run 200ns

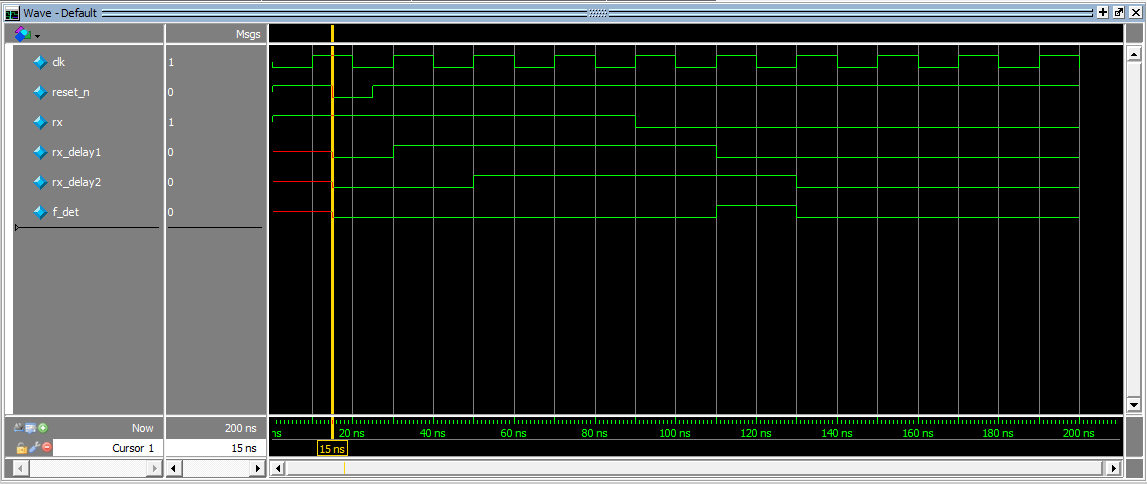

15ns : clk 에 관계없이 reset_n 을 누르면 rx_delay1, rx_delay2 가 0 으로 초기화된다.

30ns, posedge clk : rx 가 첫 번째 FF 를 지나서 rx_delay1 에 rx 값(1)이 그대로 출력된다.

50ns, posedge clk : 두 번째 FF 를 지나서 rx_delay2 에 rx_delay1 값(1)이 그대로 출력된다.

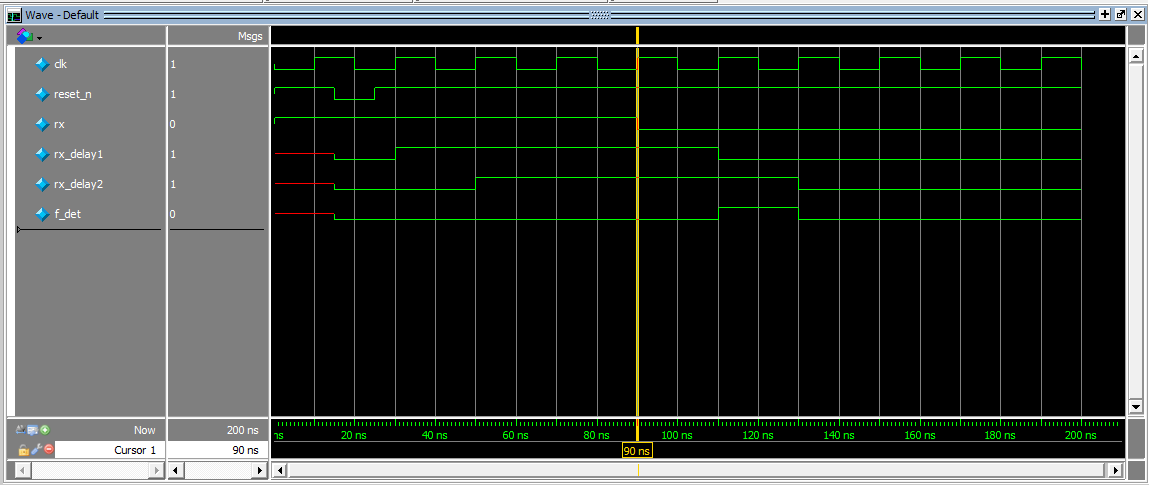

90ns : rx 의 falling edge 가 발생. FF 2개를 거치기 때문에 rx_delay1, rx_delay2 는 각각 1, 2 Period 씩 delay 가 생긴다.

110ns ~ 130ns : assign f_det = rx_delay2 & ~rx_delay1; // f_det 의 값이 1 이라면, rx 의 falling edge 가 발생했다는 사실을 확인할 수 있다.

'[Harman] 반도체 설계 > Quartus' 카테고리의 다른 글

| Quartus II project - Uart Rx Segment [1]. (0) | 2023.08.17 |

|---|---|

| Quartus II project - Simple Uart Rx. (0) | 2023.08.16 |

| Quartus II Project - notes [2] (0) | 2023.08.13 |

| Quartus II project - notes [1] (0) | 2023.08.12 |

| Quartus II project - Simple Uart Tx. (0) | 2023.08.12 |