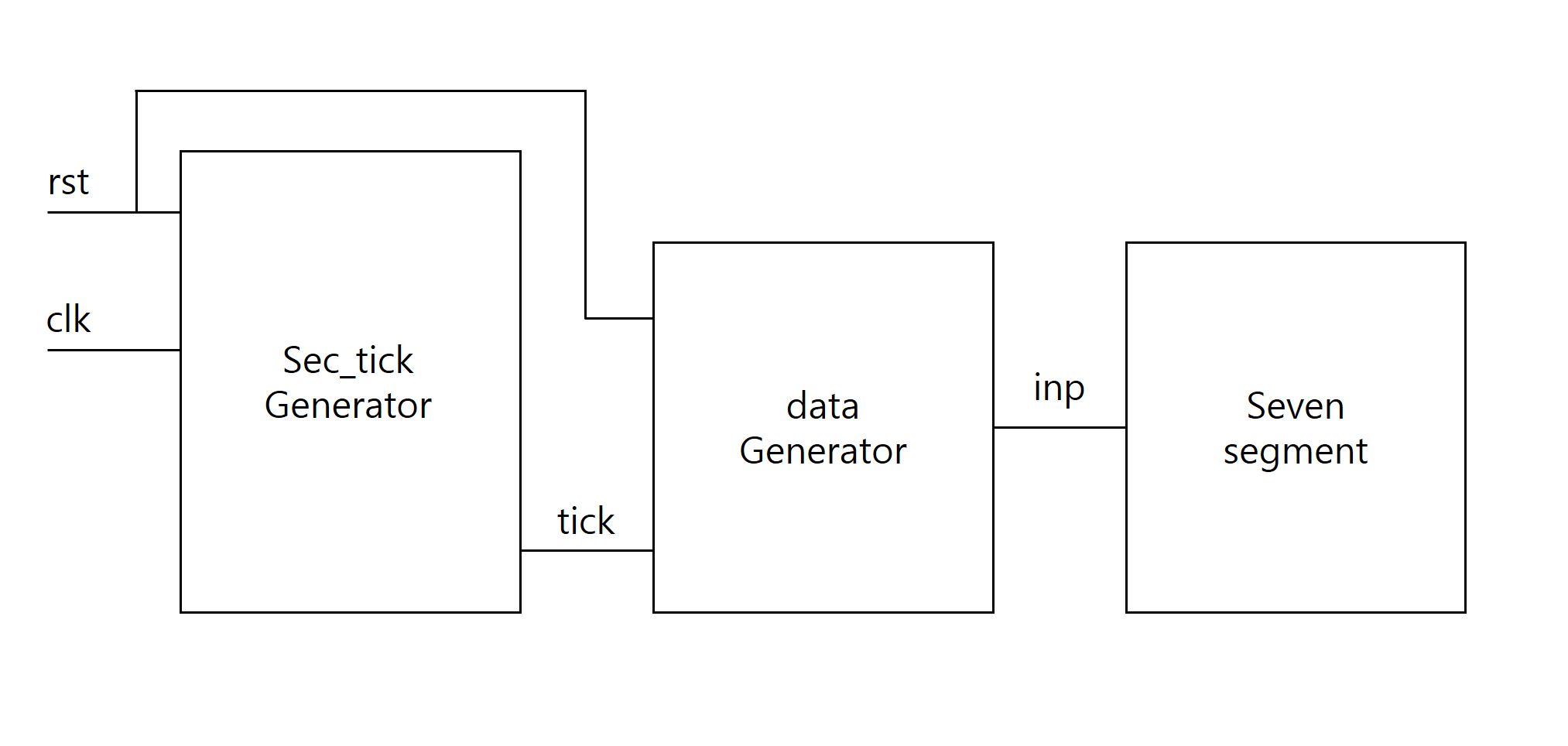

module fnd_counter (

input clk,

input reset_n,

output seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g

);

wire w_clk;

wire [3:0] w_cnt;

sec_tick_gen uSec_tick_gen (

.clk(clk),

.reset(reset_n),

.o_clk(w_clk)

);

data_gen uData_gen (

.tick(w_clk),

.reset_n(reset_n),

.cnt(w_cnt)

);

seven_segment_cntrl uSeven_segment_cntrl (

.inp(w_cnt),

.seg_a(seg_a),

.seg_b(seg_b),

.seg_c(seg_c),

.seg_d(seg_d),

.seg_e(seg_e),

.seg_f(seg_f),

.seg_g(seg_g)

);

endmodule

module seven_segment_cntrl (

input [3:0] inp,

output reg seg_a,

output reg seg_b,

output reg seg_c,

output reg seg_d,

output reg seg_e,

output reg seg_f,

output reg seg_g

);

always@(*) begin

case(inp)

4'b0000 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111110; //0

4'b0001 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0110000; //1

4'b0010 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1101101; //2

4'b0011 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111001; //3

4'b0100 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0110011; //4

4'b0101 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1011011; //5

4'b0110 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1011111; //6

4'b1000 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111111; //8

4'b1001 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110011; //9

4'b0111 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110000; //7

4'b1010 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110111; //A

4'b1011 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0011111; //b

4'b1100 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1001110; //C

4'b1101 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0111101; //d

4'b1110 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1001111; //E

4'b1111 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1000111; //F

endcase

end

endmodule

module data_gen (

input tick,

input reset_n,

output reg [3:0] cnt

);

always @(posedge tick, negedge reset_n) begin

if(!reset_n)

cnt <= 0;

else if(cnt == 16)

cnt <= 0;

else

cnt <= cnt + 4'b1;

end

endmodule

module sec_tick_gen (

input clk,

input reset,

output reg o_clk = 0

);

reg [25:0] r_counter;

always @(posedge clk, negedge reset) begin

if(!reset)

r_counter <= 0;

else if(r_counter == 49_999_999) begin

r_counter <= 0;

o_clk <= 1'b1;

end

else begin

r_counter <= r_counter + 1;

o_clk <= 1'b0;

end

end

endmodulemodule fnd_counter(

input clk,

input reset_n,

output reg seg_a,

output reg seg_b,

output reg seg_c,

output reg seg_d,

output reg seg_e,

output reg seg_f,

output reg seg_g

);

reg [3:0] cnt = 0;

reg [25:0] r_counter = 0;

reg o_clk = 0;

always @(posedge clk, negedge reset_n) begin

if(!reset_n) begin

r_counter <= 0;

cnt <= 0;

end

else if(r_counter == 49_999_999) begin

r_counter <= 0;

o_clk <= 1'b1;

cnt <= cnt + 4'b1;

end

else begin

r_counter <= r_counter + 1;

o_clk <= 1'b0;

end

end

always@(*) begin

case(cnt)

4'b0000 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111110; //0

4'b0001 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0110000; //1

4'b0010 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1101101; //2

4'b0011 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111001; //3

4'b0100 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0110011; //4

4'b0101 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1011011; //5

4'b0110 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1011111; //6

4'b0111 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110000; //7

4'b1000 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111111; //8

4'b1001 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110011; //9

4'b1010 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110111; //A

4'b1011 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0011111; //b

4'b1100 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1001110; //C

4'b1101 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0111101; //d

4'b1110 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1001111; //E

4'b1111 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1000111; //F

endcase

end

endmodule

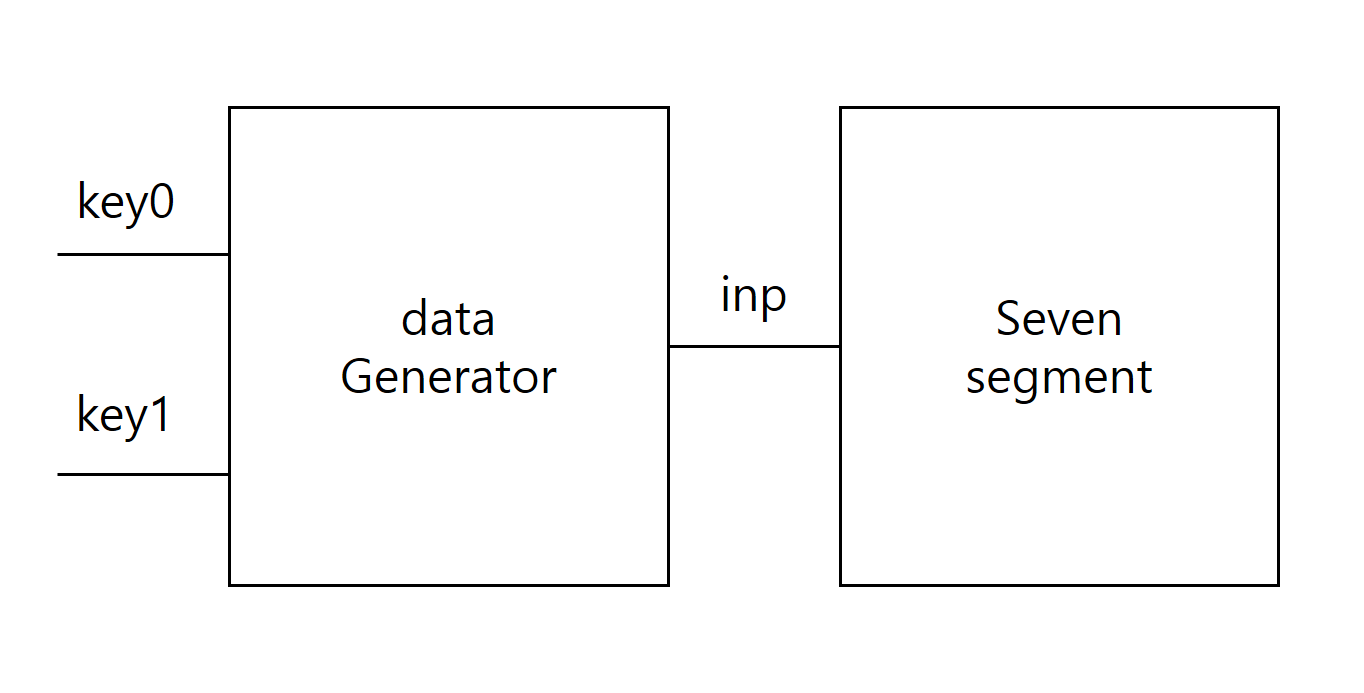

fnd_counter_sw

module fnd_counter_sw (

input reset_c, // change

input reset_n, // reset

output reg seg_a,

output reg seg_b,

output reg seg_c,

output reg seg_d,

output reg seg_e,

output reg seg_f,

output reg seg_g

);

reg [3:0] cnt = 0;

always @(negedge reset_c, negedge reset_n) begin

if(!reset_n)

cnt <= 4'b0;

else if(cnt == 16)

cnt <= 4'b0;

else

cnt <= cnt + 4'b1;

end

always @(*) begin

case (cnt)

4'b0000 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111110; //0

4'b0001 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0110000; //1

4'b0010 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1101101; //2

4'b0011 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111001; //3

4'b0100 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0110011; //4

4'b0101 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1011011; //5

4'b0110 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1011111; //6

4'b0111 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110000; //7

4'b1000 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111111; //8

4'b1001 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110011; //9

4'b1010 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110111; //A

4'b1011 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0011111; //b

4'b1100 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1001110; //C

4'b1101 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0111101; //d

4'b1110 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1001111; //E

4'b1111 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1000111; //F

endcase

end

endmodulemodule fnd_counter_sw (

input reset_c, // change

input reset_n, // reset

output reg seg_a,

output reg seg_b,

output reg seg_c,

output reg seg_d,

output reg seg_e,

output reg seg_f,

output reg seg_g

);

reg [3:0] cnt = 0;

always @(negedge reset_c, negedge reset_n) begin

if(!reset_n)

cnt <= 4'b0;

//else if(cnt == 16) can reduce the logic size

//cnt <= 4'b0;

else

cnt <= cnt + 4'b1;

end

always @(*) begin

case (cnt)

4'b0000 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111110; //0

4'b0001 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0110000; //1

4'b0010 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1101101; //2

4'b0011 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111001; //3

4'b0100 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0110011; //4

4'b0101 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1011011; //5

4'b0110 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1011111; //6

4'b0111 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110000; //7

4'b1000 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111111; //8

4'b1001 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110011; //9

4'b1010 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1110111; //A

4'b1011 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0011111; //b

4'b1100 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1001110; //C

4'b1101 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b0111101; //d

4'b1110 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1001111; //E

4'b1111 : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1000111; //F

default : {seg_a, seg_b, seg_c, seg_d, seg_e, seg_f, seg_g} = ~7'b1111110; //0

endcase

end

endmodule

'[Harman] 반도체 설계 > Quartus' 카테고리의 다른 글

| Quartus II Project - notes [2] (0) | 2023.08.13 |

|---|---|

| Quartus II project - notes [1] (0) | 2023.08.12 |

| Quartus II project - Simple Uart Tx. (0) | 2023.08.12 |

| Quartus II Project - adder, mult4x4 (0) | 2023.07.27 |

| Quartus II Project - mux4, shifter (0) | 2023.07.27 |