Avalon_Model, r/w

`timescale 1ns/1ns

// Avalon Bus Model for Simulation

module avalon_model (

input clk,

input rst,

// avalon Bus

output reg [31:0] mp_addr,

output reg [ 3:0] mp_bEn,

output reg mp_rD,

output reg mp_wR,

input mp_waitR,

input [31:0] mp_rData,

output reg [31:0] mp_wData

);

parameter FF = 1; // delay

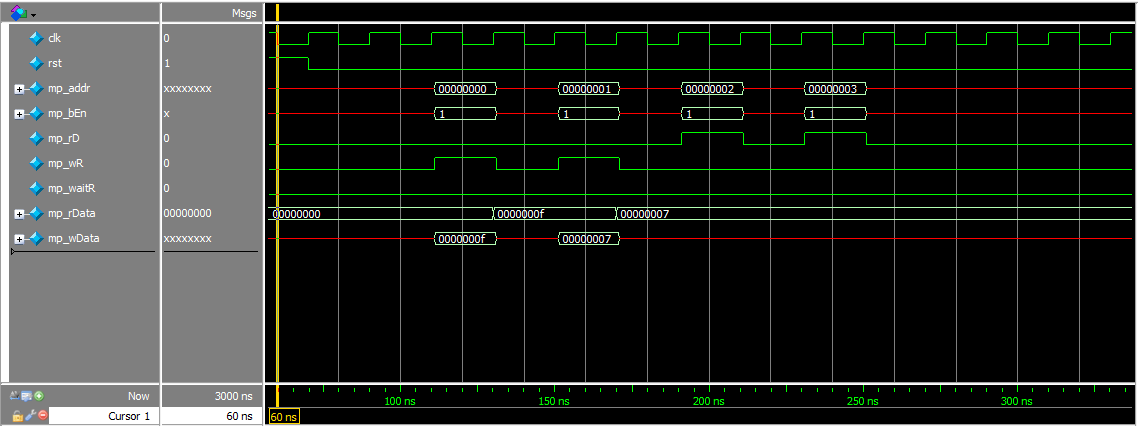

initial begin

mp_addr = 32'hx;

mp_bEn = 4'bx;

mp_rD = 1'b0;

mp_wR = 1'b0;

mp_wData = 32'hx;

repeat(5) @(posedge clk);

avalon_write(32'h0000, 32'hf);

avalon_write(32'h0001, 32'h7);

avalon_read(32'h0002);

avalon_read(32'h0003);

end

task avalon_write;

input [31:0] wAddr;

input [31:0] wData;

begin

@(posedge clk);

#(FF);

mp_addr = wAddr;

mp_bEn = 4'b0001;

mp_wR = 1'b1;

mp_wData = wData;

@(posedge clk);

while (mp_waitR) begin

@(posedge clk);

end

#(FF);

mp_addr = 32'hx;

mp_bEn = 4'bx;

mp_rD = 1'b0;

mp_wR = 1'b0;

mp_wData = 32'hx;

end

endtask

task avalon_read;

input [31:0] rAddr;

begin

@(posedge clk);

#(FF);

mp_addr = rAddr;

mp_bEn = 4'b0001;

mp_rD = 1'b1;

@(posedge clk);

while (mp_waitR) begin

@(posedge clk);

end

$display("AV rAddr 0x%x, rData 0x%x", mp_addr, mp_rData);

#(FF);

mp_addr = 32'hx;

mp_bEn = 4'bx;

mp_rD = 1'b0;

end

endtask

endmodule`timescale 1 ns / 1 ps

module tb_avalon_model();

reg clk ;

reg rst ;

wire [31:0] mp_addr ;

wire [ 3:0] mp_bEn ;

wire mp_rD ;

wire mp_wR ;

reg mp_waitR ;

reg [31:0] mp_rData ;

wire [31:0] mp_wData ;

avalon_model uAvalon_model_0 (

.clk (clk ),

.rst (rst ),

.mp_addr (mp_addr ),

.mp_bEn (mp_bEn ),

.mp_rD (mp_rD ),

.mp_wR (mp_wR ),

.mp_waitR(mp_waitR),

.mp_rData(mp_rData),

.mp_wData(mp_wData)

);

//parallel

initial fork

clk_gen_task();

reset_task();

data_task();

join

// 50Mhz, 20ns

task clk_gen_task;

begin

clk = 1'b0;

forever #10 clk = ~clk;

end

endtask

task reset_task;

begin

rst = 1'b0;

repeat(2) @(posedge clk);

rst = 1'b1;

repeat(2) @(posedge clk);

rst = 1'b0;

end

endtask

task data_task;

begin

#75;

mp_rData = 32'h11223344;

end

endtask

endmodulevlib work

vlog avalon_model.v tb_avalon_model.v

vsim -t ns work.tb_avalon_model

view wave

add wave -radix hex /clk

add wave -radix hex /rst

add wave -radix hex /mp_addr

add wave -radix hex /mp_bEn

add wave -radix hex /mp_rD

add wave -radix hex /mp_wR

add wave -radix hex /mp_waitR

add wave -radix hex /mp_rData

add wave -radix hex /mp_wData

run 500 ns

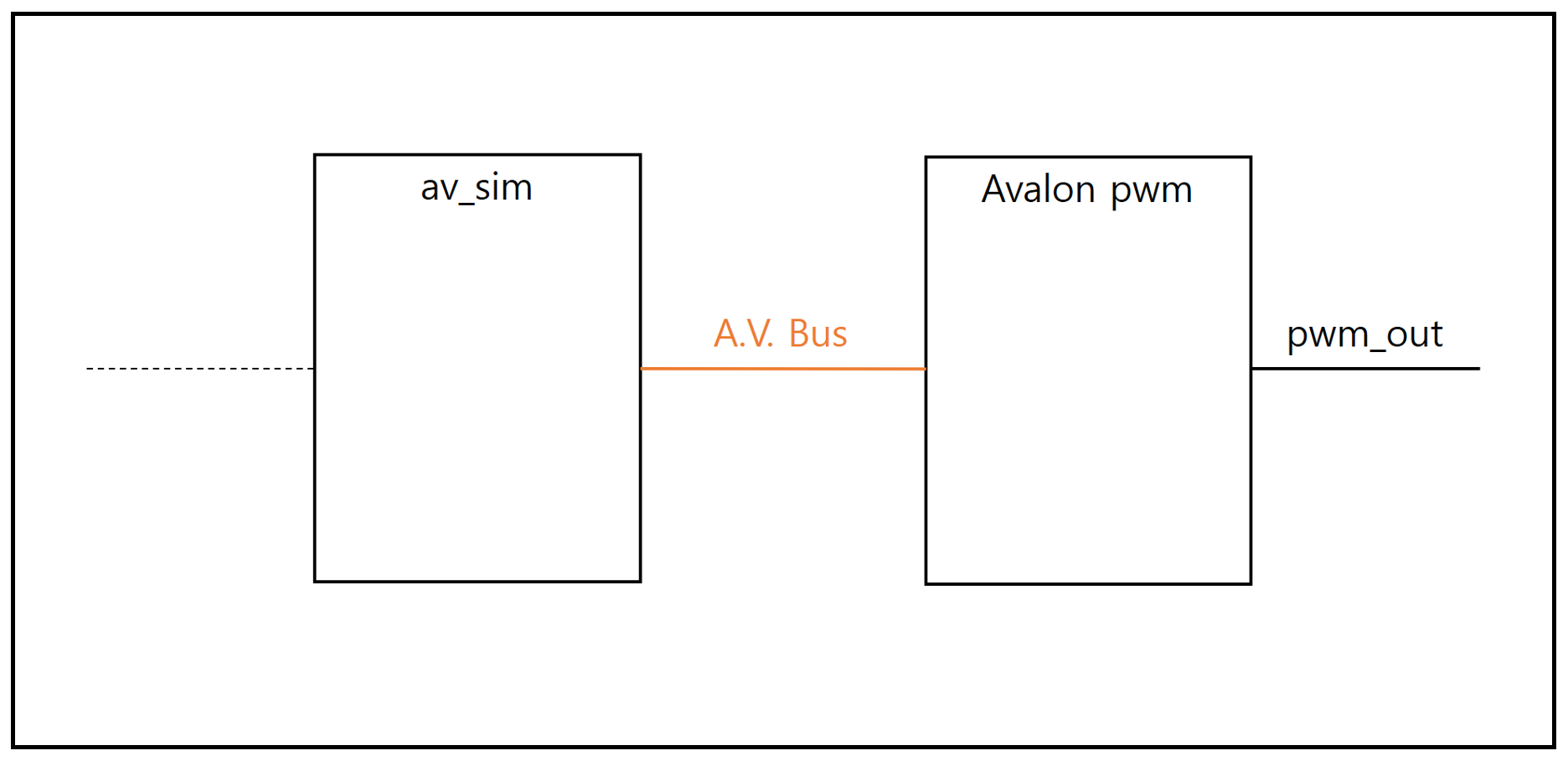

Avalon_Model, My_reg

`timescale 1 ns / 1 ps

module tb_avalon_model();

reg clk ;

reg rst ;

wire [31:0] mp_addr ;

wire [ 3:0] mp_bEn ;

wire mp_rD ;

wire mp_wR ;

wire mp_waitR ;

wire [31:0] mp_rData ;

wire [31:0] mp_wData ;

//Master

avalon_model uAvalon_model_0 (

.clk (clk ),

.rst (rst ),

.mp_addr (mp_addr ),

.mp_bEn (mp_bEn ),

.mp_rD (mp_rD ),

.mp_wR (mp_wR ),

.mp_waitR(mp_waitR),

.mp_rData(mp_rData),

.mp_wData(mp_wData)

);

My_reg uMy_reg_0(

.clk (clk ),

.rst (rst ),

.addr (mp_addr ),

.bEn (mp_bEn ),

.rD (mp_rD ),

.wR (mp_wR ),

.waitR(mp_waitR),

.rData(mp_rData),

.wData(mp_wData)

);

//parallel

initial fork

clk_gen_task();

reset_task();

join

// 50Mhz, 20ns

task clk_gen_task;

begin

clk = 1'b0;

forever #10 clk = ~clk;

end

endtask

task reset_task;

begin

rst = 1'b0;

repeat(2) @(posedge clk);

rst = 1'b1;

repeat(2) @(posedge clk);

rst = 1'b0;

end

endtask

endmodule

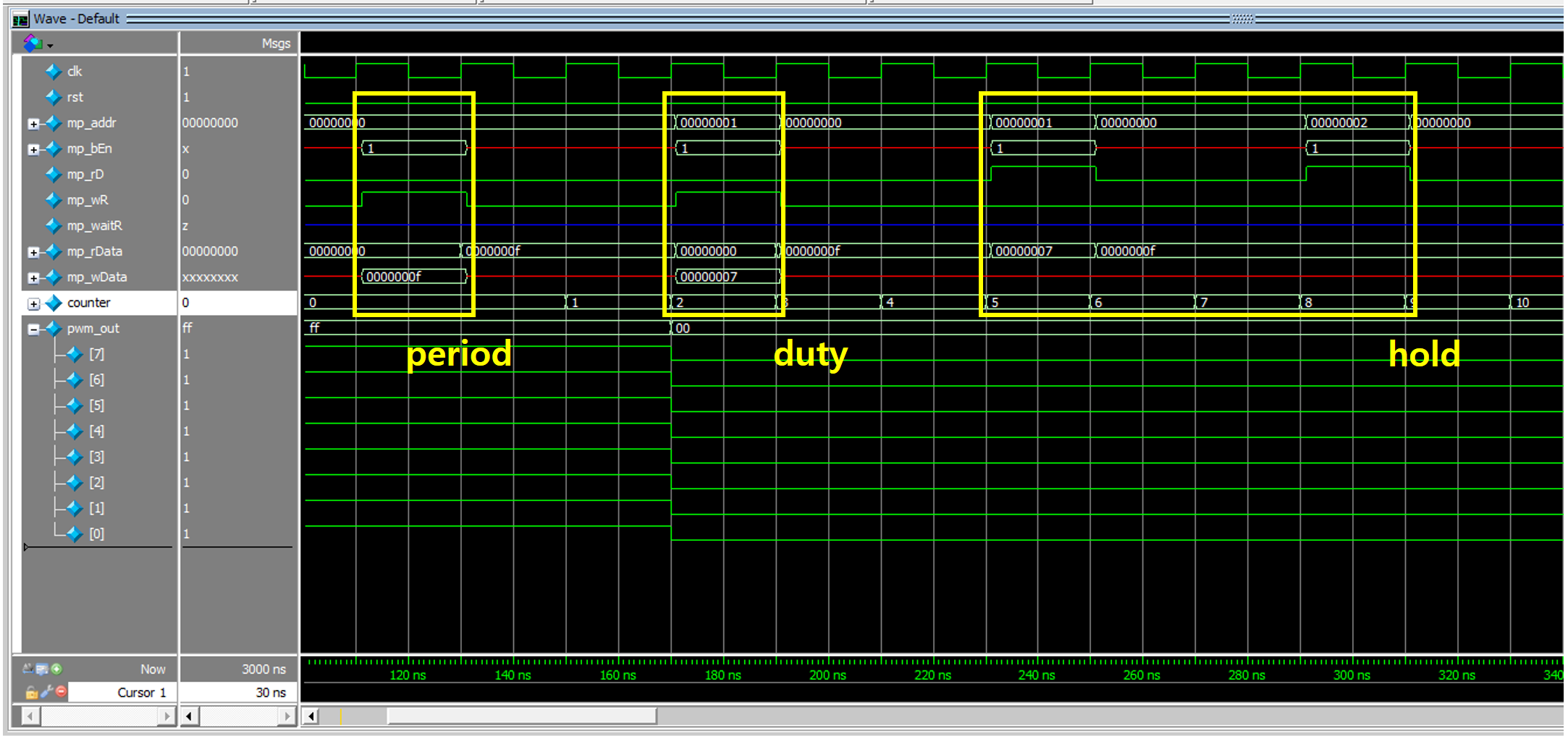

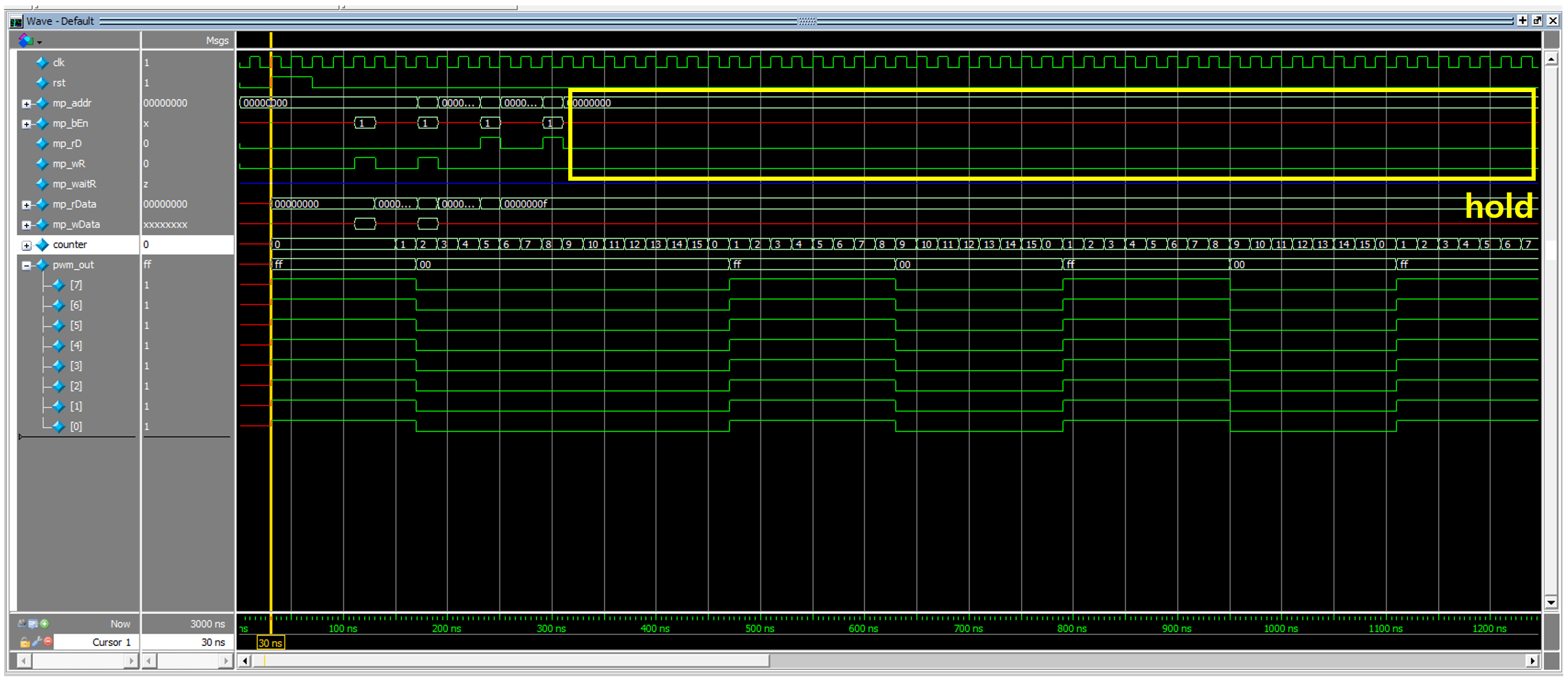

Avalon_Model, My_pwm

`timescale 1ns/1ns

// Avalon Bus Model for Simulation

module avalon_model (

input clk,

input rst,

// avalon Bus

output reg [31:0] mp_addr,

output reg [ 3:0] mp_bEn,

output reg mp_rD,

output reg mp_wR,

input mp_waitR,

input [31:0] mp_rData,

output reg [31:0] mp_wData

);

parameter FF = 1; // delay

initial begin

mp_addr = 32'h0;

mp_bEn = 4'bx;

mp_rD = 1'b0;

mp_wR = 1'b0;

mp_wData = 32'hx;

repeat(5) @(posedge clk);

avalon_write(32'h0000, 32'hf);

avalon_write(32'h0001, 32'h7);

avalon_read(32'h0002);

avalon_read(32'h0003);

end

task avalon_write;

input [31:0] wAddr;

input [31:0] wData;

begin

@(posedge clk);

#(FF);

mp_addr = wAddr;

mp_bEn = 4'b0001;

mp_wR = 1'b1;

mp_wData = wData;

@(posedge clk);

while (mp_waitR) begin

@(posedge clk);

end

#(FF);

mp_addr = 32'h0;

mp_bEn = 4'bx;

mp_rD = 1'b0;

mp_wR = 1'b0;

mp_wData = 32'hx;

end

endtask

task avalon_read;

input [31:0] rAddr;

begin

@(posedge clk);

#(FF);

mp_addr = rAddr;

mp_bEn = 4'b0001;

mp_rD = 1'b1;

@(posedge clk);

while (mp_waitR) begin

@(posedge clk);

end

$display("AV rAddr 0x%x, rData 0x%x", mp_addr, mp_rData);

#(FF);

mp_addr = 32'h0;

mp_bEn = 4'bx;

mp_rD = 1'b0;

end

endtask

endmodule

`timescale 1 ns / 1 ps

module tb_avalon_model();

reg clk ;

reg rst ;

wire [31:0] mp_addr ;

wire [ 3:0] mp_bEn ;

wire mp_rD ;

wire mp_wR ;

wire mp_waitR ;

wire [31:0] mp_rData ;

wire [31:0] mp_wData ;

//Master

avalon_model uAvalon_model_0 (

.clk (clk ),

.rst (rst ),

.mp_addr (mp_addr ),

.mp_bEn (mp_bEn ),

.mp_rD (mp_rD ),

.mp_wR (mp_wR ),

.mp_waitR(mp_waitR),

.mp_rData(mp_rData),

.mp_wData(mp_wData)

);

avalon_pwm uAvalon_pwm_0 (

.clk (clk ),

.wr_data(mp_wData),

.wr_n (!mp_wR ),

.addr (mp_addr ),

.clr_n (!rst ),

.rd_data(mp_rData),

.pwm_out(pwm_out )

);

//parallel

initial fork

clk_gen_task();

reset_task();

join

// 50Mhz, 20ns

task clk_gen_task;

begin

clk = 1'b0;

forever #10 clk = ~clk;

end

endtask

task reset_task;

begin

rst = 1'b0;

repeat(2) @(posedge clk);

rst = 1'b1;

repeat(2) @(posedge clk);

rst = 1'b0;

end

endtask

endmodulevlib work

vlog avalon_model.v tb_avalon_model.v avalon_pwm.v

vsim -t ns work.tb_avalon_model

view wave

add wave -radix hex /clk

add wave -radix hex /rst

add wave -radix hex /mp_addr

add wave -radix hex /mp_bEn

add wave -radix hex /mp_rD

add wave -radix hex /mp_wR

add wave -radix hex /mp_waitR

add wave -radix hex /mp_rData

add wave -radix hex /mp_wData

add wave -radix unsigned /tb_avalon_model/uAvalon_pwm_0/counter

add wave -radix hex /pwm_out

run 3000 nsQuartus II project - Avalon pwm.

PWM : Pulse Width Modulation. Required Register : 8 bit duty, 8 bit div(period) Why 8 Bit? : Computer Architecture 에서 8bit CPU라고 하면 ALU, 레지스터, 데이터 버스 등의 처리 단위가 8비트로 된 CPU를 말한다. Imbedded System 과

lrsfe.tistory.com

'[Harman] 반도체 설계 > Avalon' 카테고리의 다른 글

| SoC Design with Nios II Processor. (2) | 2023.10.21 |

|---|---|

| Avalon Memory-Mapped Interfaces - pwm. (0) | 2023.10.16 |

| Avalon Memory-Mapped Interfaces - Register. (0) | 2023.10.16 |

| Avalon Memory-Mapped Interfaces. (0) | 2023.10.14 |

| Avalon - Nios II processor : GPIO (0) | 2023.10.11 |