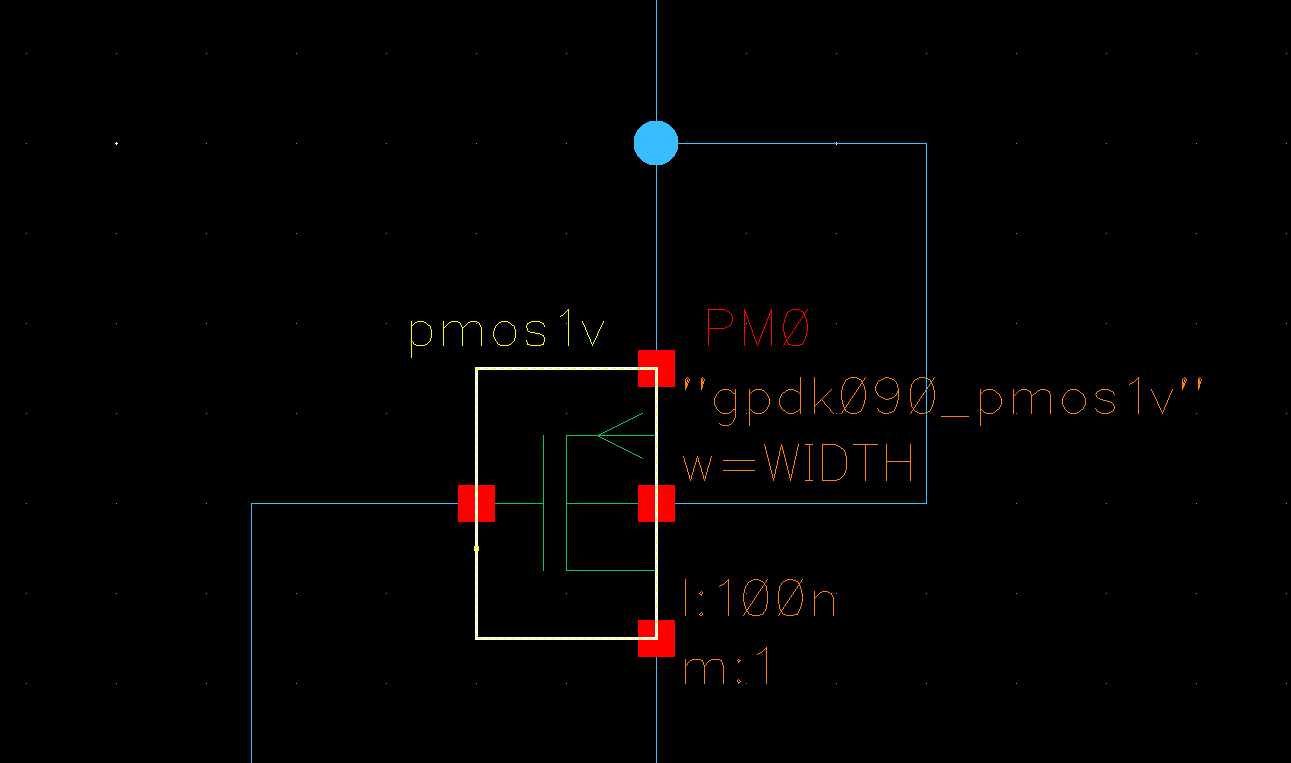

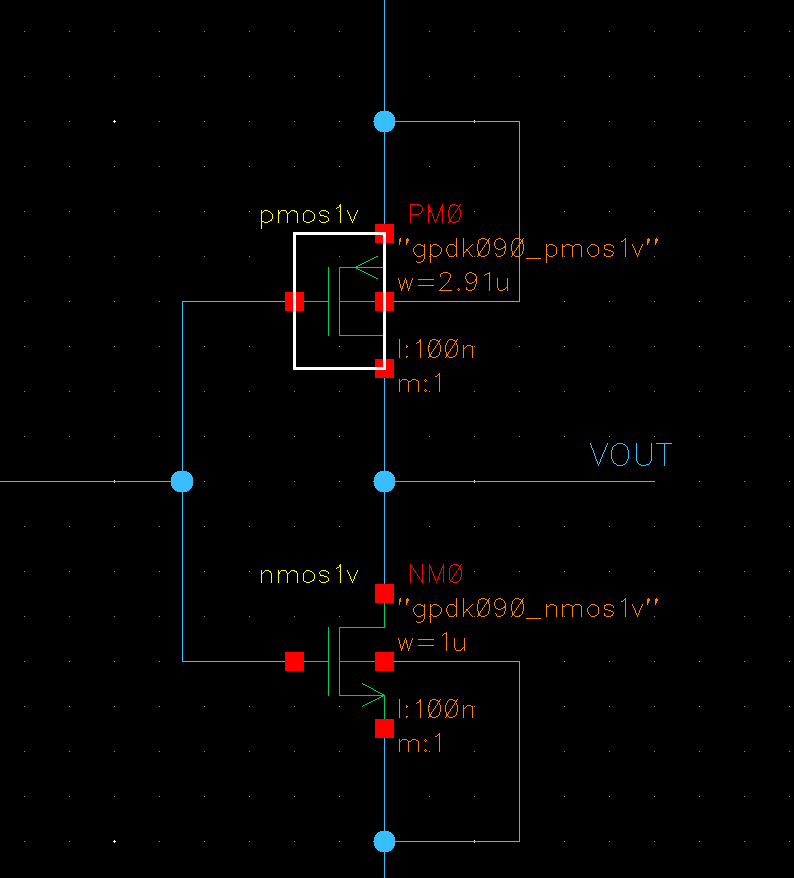

Mobility 차로 인하여 N-MOS 와 P-MOS 는 서로 다른 WIDTH 를 가진다.

N-MOS 의 WIDTH, 1um 를 기준으로, P-MOS 의 WIDTH 를 변수로 둔다.

Check and Save.

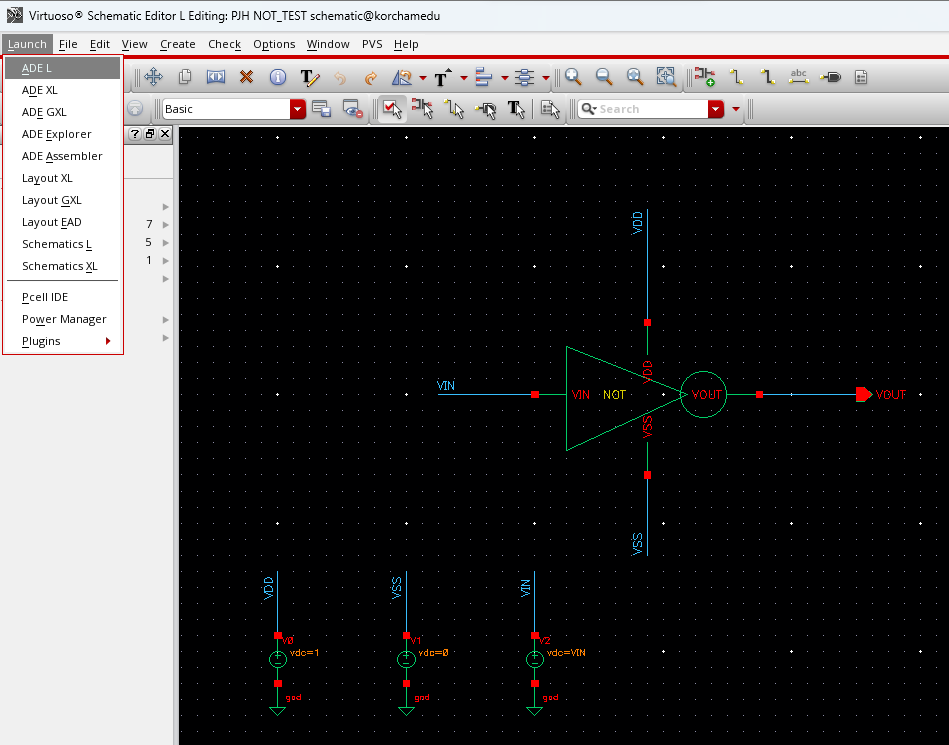

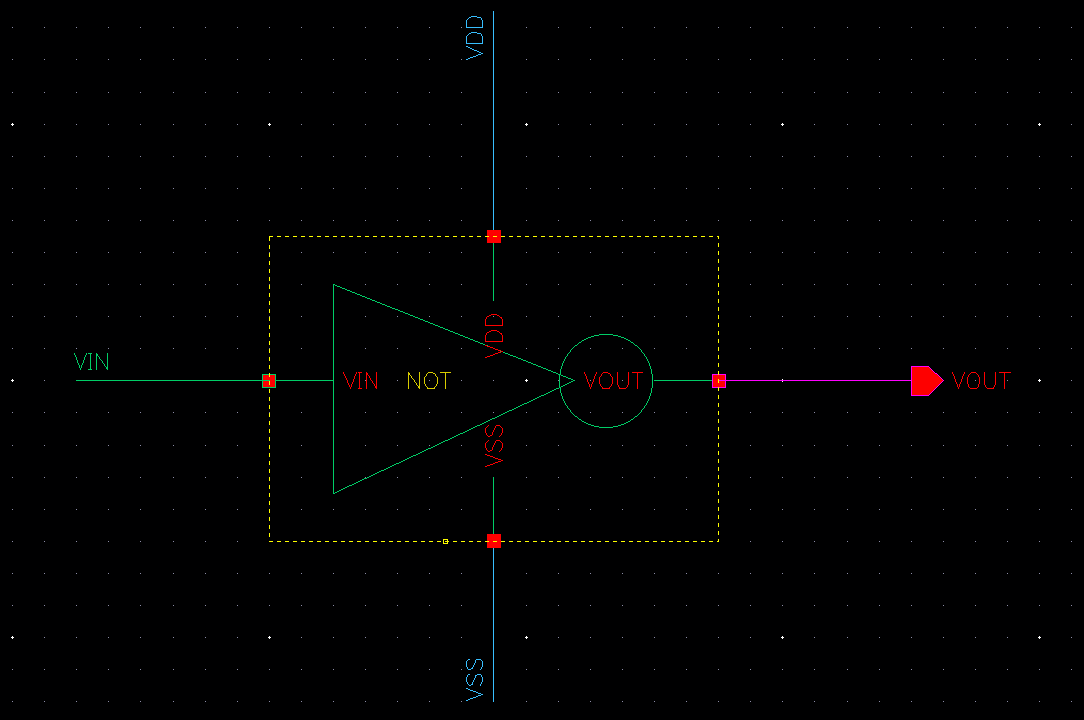

NOT_TEST Schematic.

Simulation.

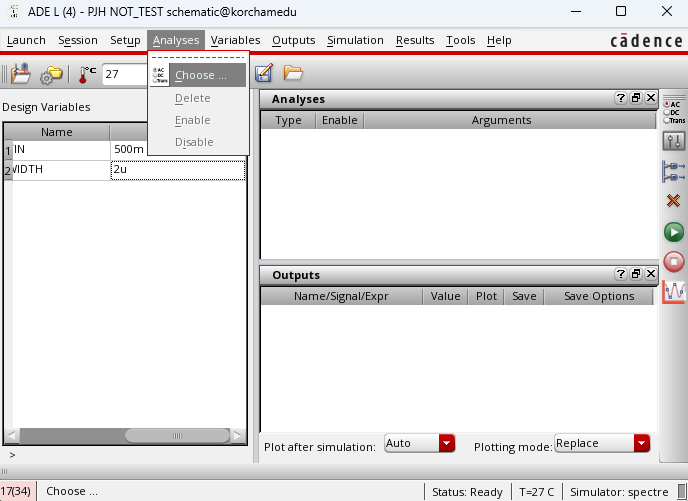

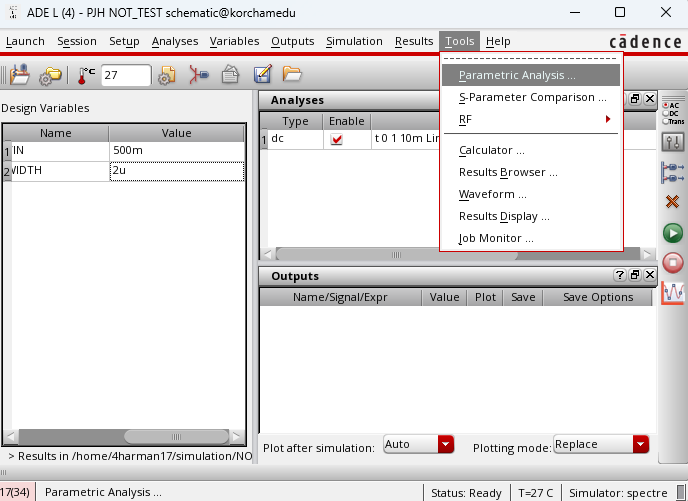

Launch - ADE_L

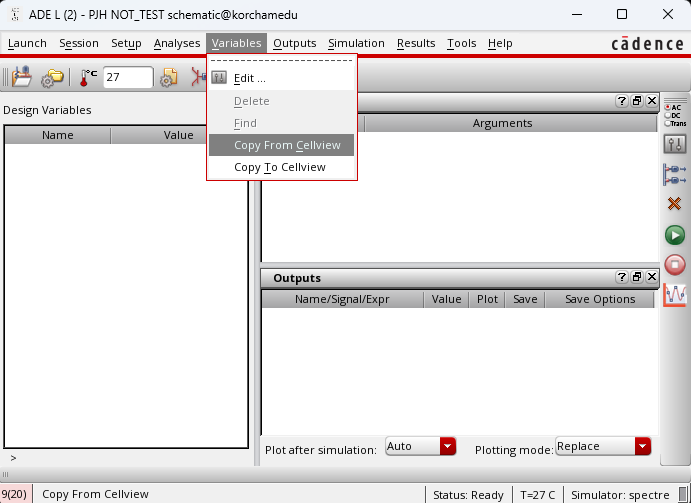

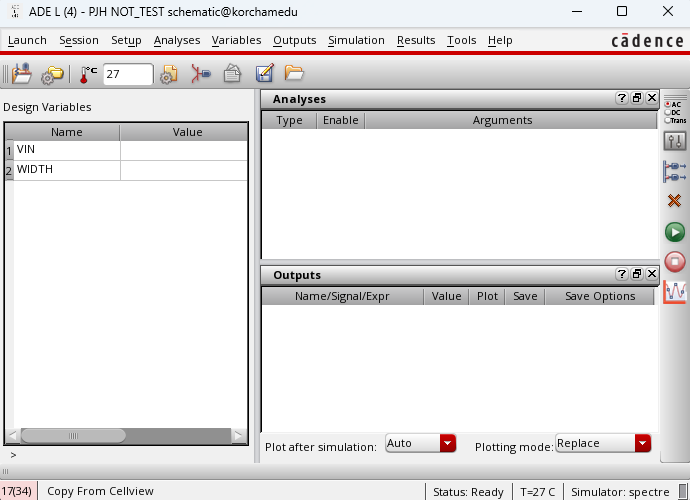

Variables - Copy From Cellview.

VIN 에 500m

WIDTH 에 2u

Simulation 을 통해 다시 조정할 값이기 때문에 아무 의미 없다.

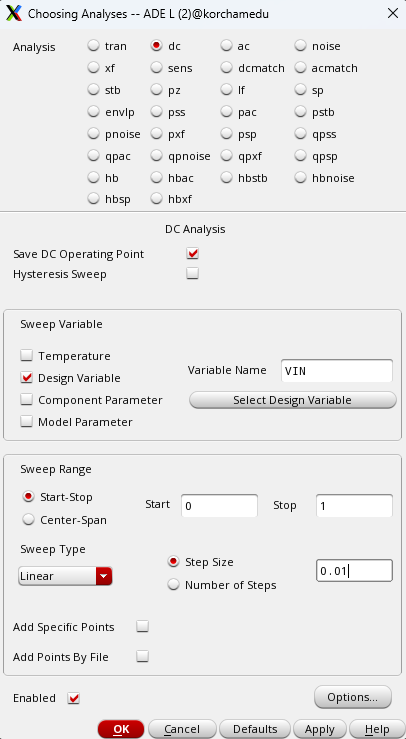

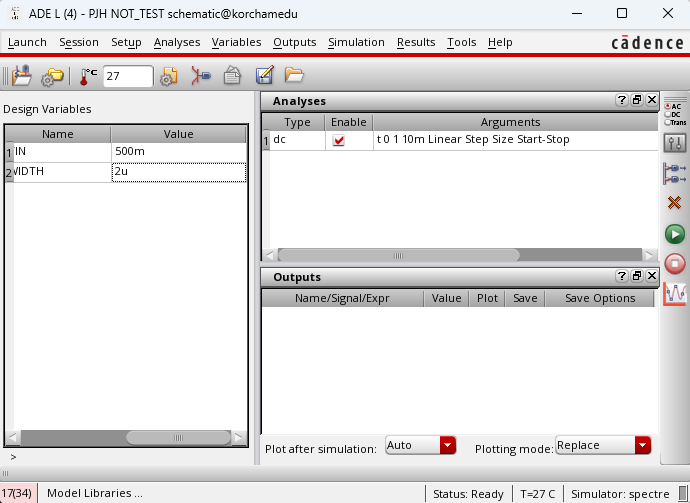

Analyses - Choose

VIN 은 0V 부터 1V 까지 10mV step 으로 진행.

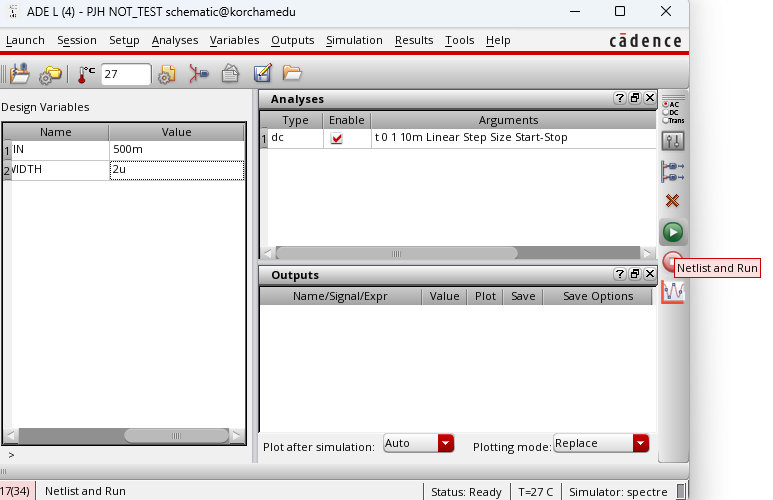

다른 방법으로, Simulation - Netlist and Run

Errors: 0 Warnings: 0

...successful.

compose simulator input file...

...successful.

start simulator if needed...

...successful.

simulate...

INFO (ADE-3071): Simulation completed successfully.

reading simulation data...

...successful.

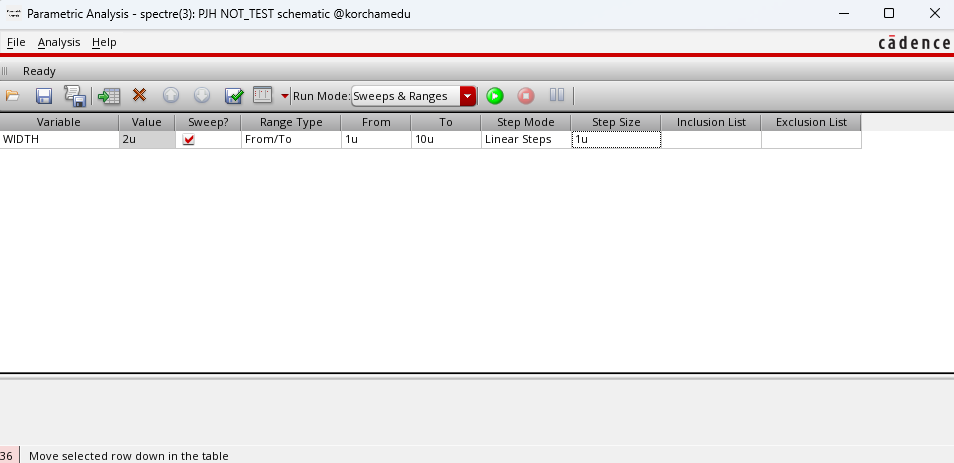

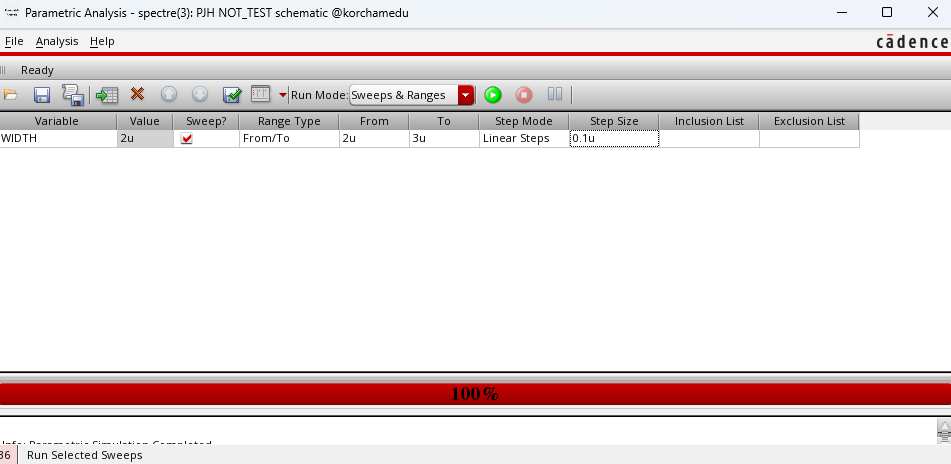

Simulation 변수 값 조정.

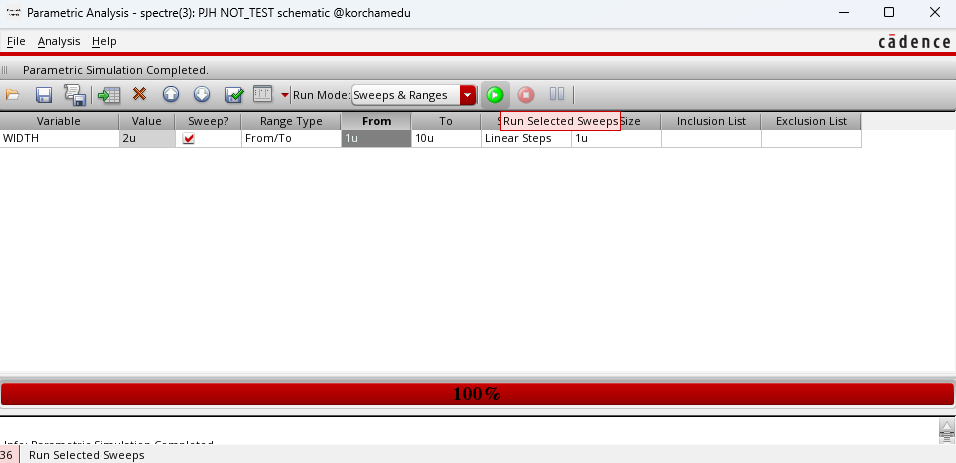

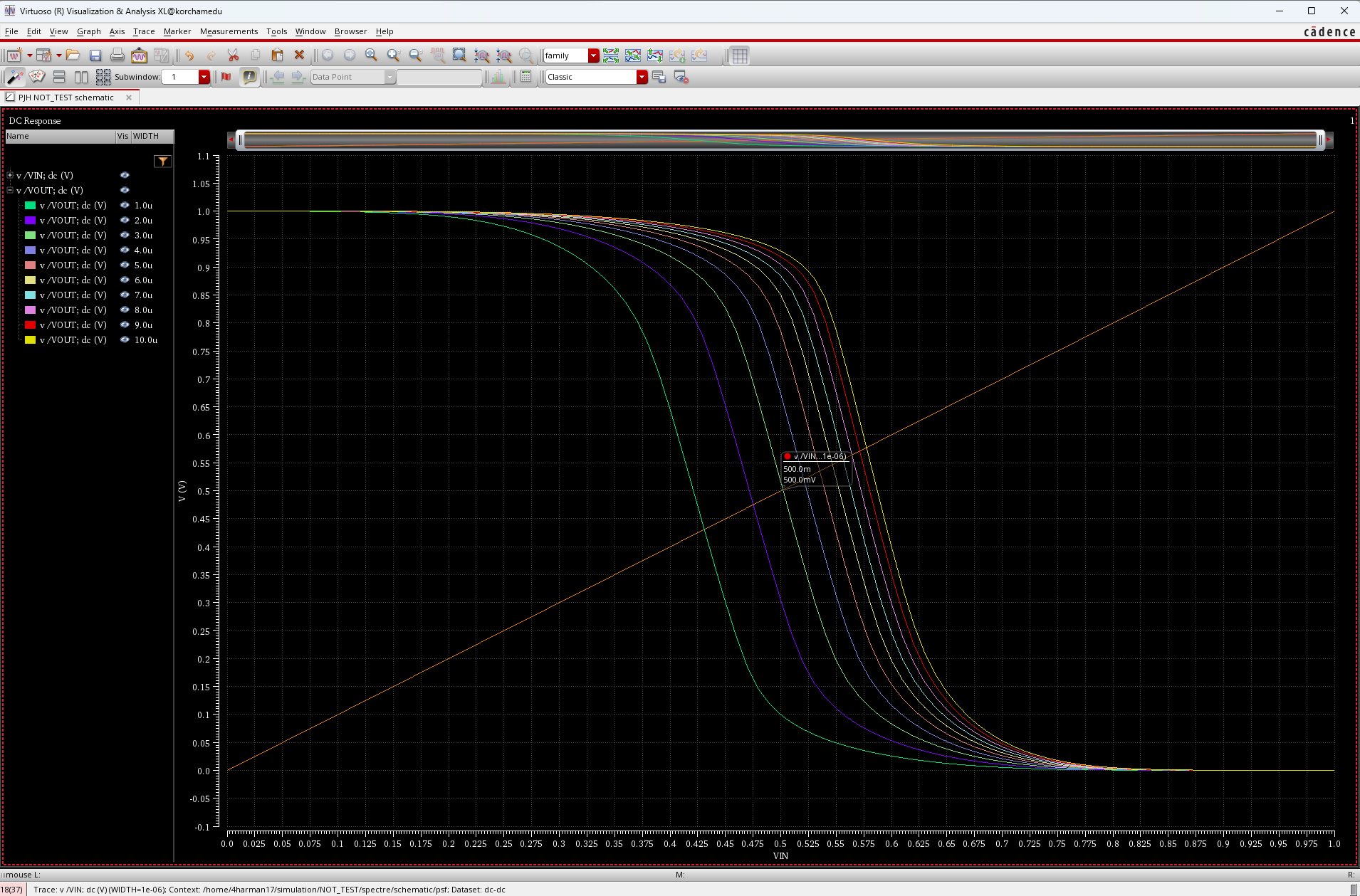

P-MOS 의 WIDTH 를 1u ~ 10u 범위에서 1u step 으로 Simulation 진행.

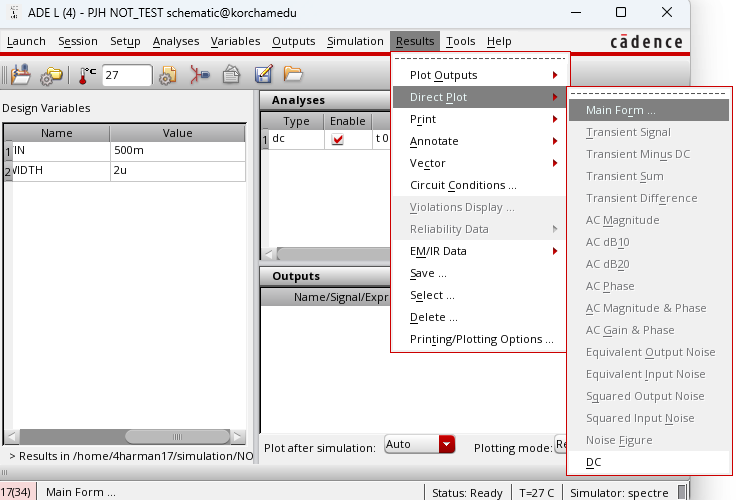

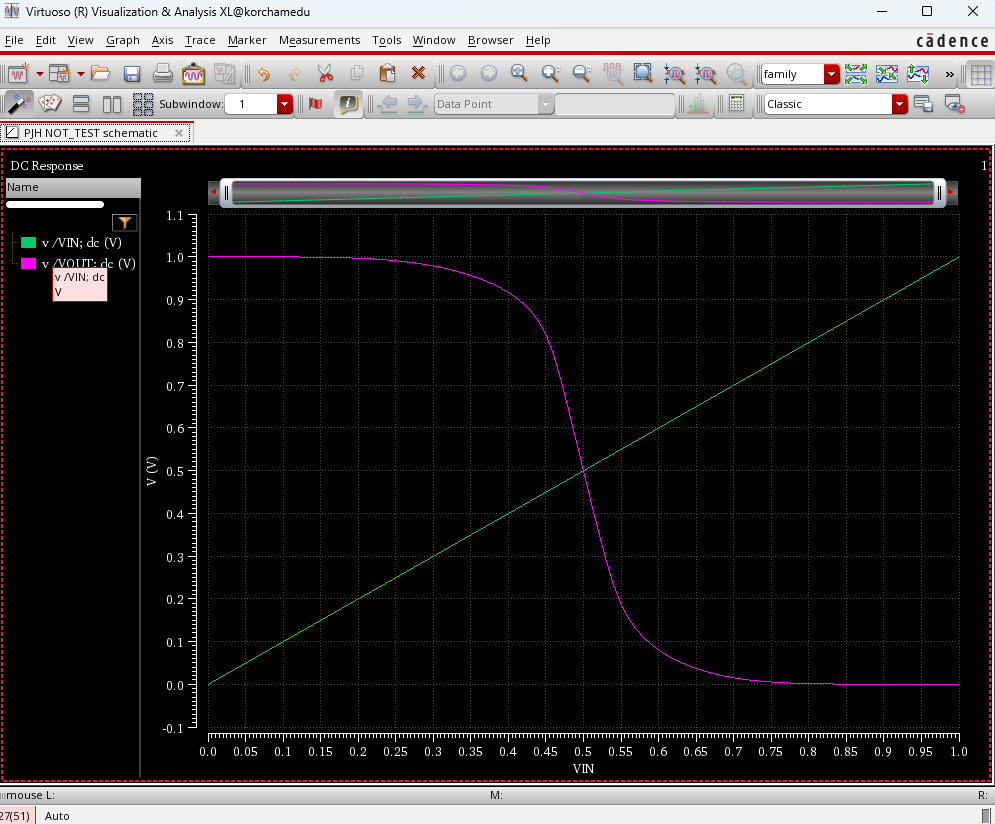

Simulation 결과 확인.

Schematic 창에서 VIN, VOUT 선택.

VIN, VOUT 의 0.5V 교차점이 2u 와 3u 사이에 있음을 확인.

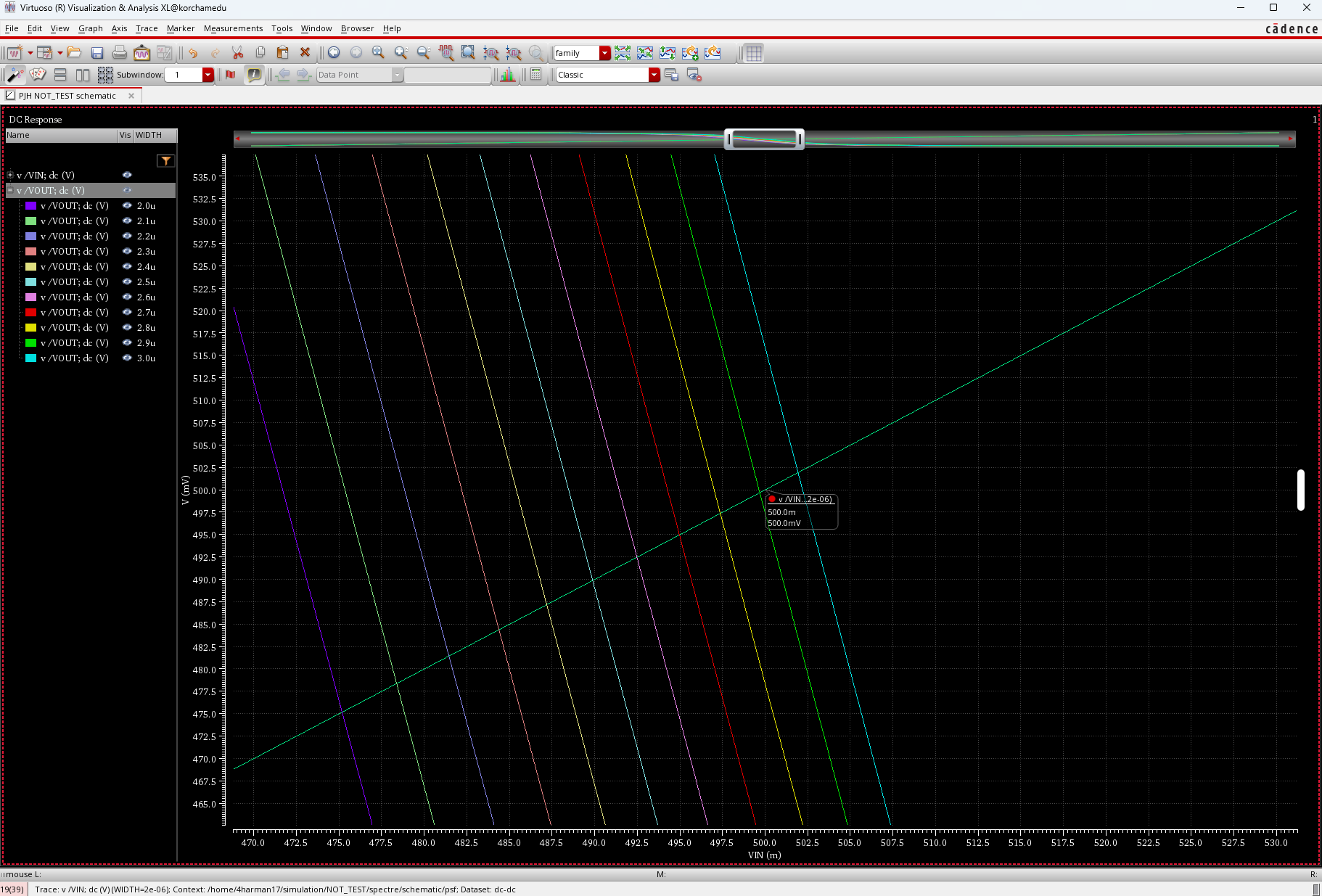

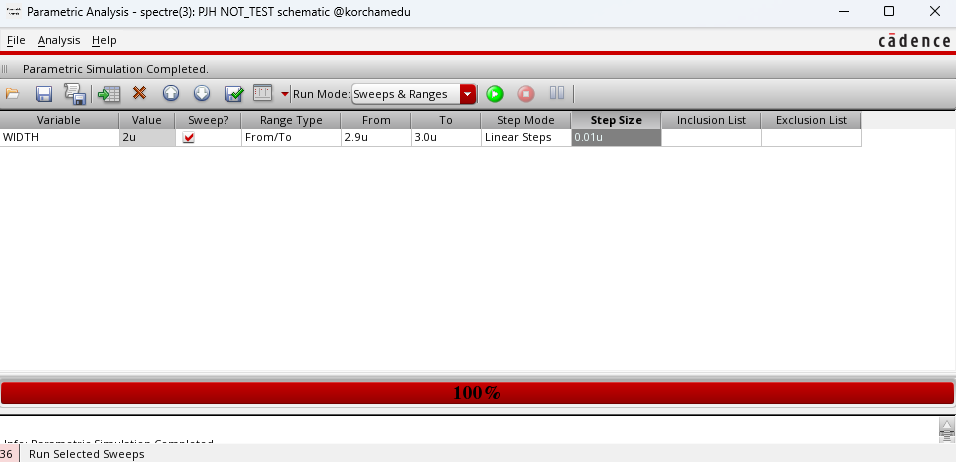

범위 조정 후 Simulation.

2.9u ~ 3.0u

2.91u

NOT Gate Logic 의 Schematic 창에서 WIDTH = 2.91u 로 변경 후 Check and Save.

Symbol, NOT_TEST Check and Save 후, 다시 Simulation 진행.

끝.

'[Harman] 반도체 설계 > Full Custom IC' 카테고리의 다른 글

| Full Custom IC - Logic Gate Lay-out. (0) | 2023.07.09 |

|---|---|

| Full Custom IC - Logic Gate Schematic & Simulation Results. (0) | 2023.07.09 |

| Full Custom IC - Logic Gate Symbol. (0) | 2023.07.09 |

| Full Custom IC - Logic Gate Schematic. (0) | 2023.07.08 |

| Full Custom IC - Virtuoso. (0) | 2023.07.08 |