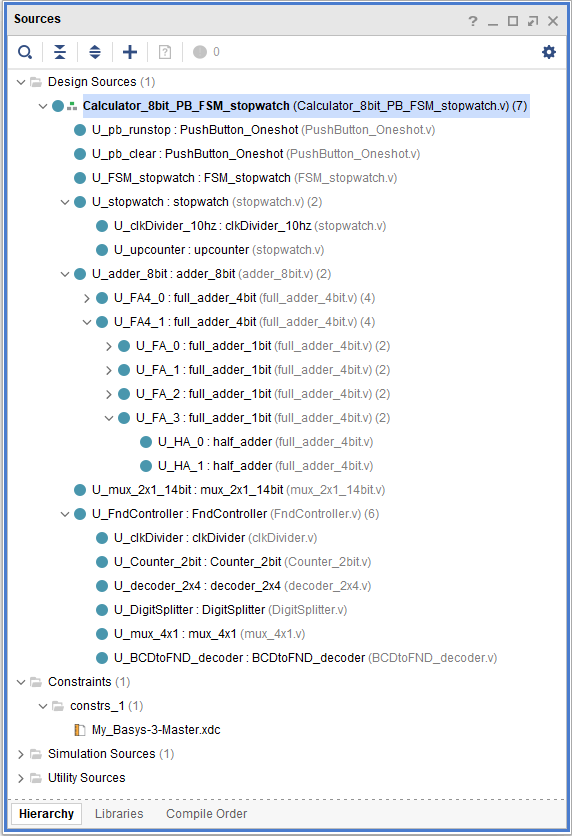

Calculator_8bit_PB_FSM_stopwatch.v

`timescale 1ns / 1ps

module Calculator_8bit_PB_FSM_stopwatch(

input clk,

input reset,

input [7:0] i_a,

input [7:0] i_b,

input i_pbrunstop,

input i_pbclear,

output [3:0] o_digitSel,

output [7:0] o_fndFont

);

wire [8:0] w_sum;

wire w_stoprun, w_clear;

wire [13:0] w_stopwatchValue, w_FndsourceValue;

wire w_pbrunstop, w_pbclear;

PushButton_Oneshot U_pb_runstop(clk, i_pbrunstop, reset, w_pbrunstop);

PushButton_Oneshot U_pb_clear(clk, i_pbclear, reset, w_pbclear);

FSM_stopwatch U_FSM_stopwatch(clk, reset, w_pbrunstop, w_pbclear, w_stoprun, w_clear);

stopwatch U_stopwatch(clk, reset, w_stoprun, w_clear, w_stopwatchValue);

adder_8bit U_adder_8bit(i_a, i_b, w_sum[7:0], w_sum[8]);

mux_2x1_14bit U_mux_2x1_14bit(i_b[7], {5'b0, w_sum}, w_stopwatchValue, w_FndsourceValue);

FndController U_FndController(clk, reset, w_FndsourceValue, o_digitSel, o_fndFont);

endmodule

PushButton_Oneshot.v

(clkDivider_100hz, de-bounce, one-shot)

`timescale 1ns / 1ps

module PushButton_Oneshot(

input clk,

input i_pb,

input reset,

output o_pb

);

// clkDivider_100hz

reg r_clk_100hz;

reg [31:0] r_counter = 0;

always@(posedge clk, posedge reset) begin // Divider 100hz

if(reset) begin

r_counter <= 0;

end

else begin

if(r_counter == 500_000 - 1) begin //duty cycle 50%

r_counter = 0;

r_clk_100hz <= ~r_clk_100hz;

end

else begin

r_counter <= r_counter + 1;

end

end

end

//de-bounce

reg [1:0] r_debounce = 2'b00; //DFF

always @(posedge r_clk_100hz, posedge reset) begin

if(reset) begin

r_debounce <= 2'b00;

end

else begin

r_debounce[0] <= i_pb;

r_debounce[1] <= r_debounce[0];

end

end

// one shot

reg r_oneshot = 1'b0;

always@(posedge clk, posedge reset) begin

if(reset) begin

r_oneshot <= 1'b0;

end

else begin

r_oneshot <= r_debounce[1];

end

end

assign o_pb = r_debounce[1] & ~r_oneshot;

endmodule

FSM_stopwatch.v

`timescale 1ns / 1ps

module FSM_stopwatch(

input clk,

input reset,

input i_stoprunSW,

input i_clearSW,

output reg o_stoprun,

output reg o_clear

);

parameter S_STOP = 2'd0, S_RUN = 2'd1, S_CLEAR = 2'd2;

reg [1:0] state = S_STOP, nextState ;

always @(posedge clk, posedge reset) begin

if(reset) state <= S_STOP;

else state <= nextState;

end

always @(*) begin

case (state)

S_STOP : begin

if(i_stoprunSW) nextState <= S_RUN;

else if(i_clearSW) nextState <= S_CLEAR;

else nextState <= S_STOP;

end

S_RUN : begin

if(!i_stoprunSW) nextState <= S_STOP;

else nextState <= S_RUN;

end

S_CLEAR : begin

if(!i_clearSW) nextState <= S_STOP;

else nextState <= S_CLEAR;

end

default : nextState <= S_STOP;

endcase

end

always @(*) begin

case (state)

S_STOP : begin

o_stoprun = 1'b0;

o_clear = 1'b0;

end

S_RUN : begin

o_stoprun = 1'b1;

o_clear = 1'b0;

end

S_CLEAR : begin

o_stoprun = 1'b0;

o_clear = 1'b1;

end

default : begin

o_stoprun = 1'b0;

o_clear = 1'b0;

end

endcase

end

endmodule

stopwatch.v

(clkDivider_10hz, upcounter)

`timescale 1ns / 1ps

module stopwatch(

input clk,

input reset,

input i_run_stop,

input i_clear,

output [13:0] o_upCounter

);

wire w_clk;

clkDivider_10hz U_clkDivider_10hz(

.clk(clk),

.reset(reset),

.i_clear(i_clear),

.i_enable(i_run_stop),

.o_clk(w_clk)

);

upcounter U_upcounter(

.clk(w_clk),

.reset(reset),

.i_clear(i_clear),

.o_upCounter(o_upCounter)

);

endmodule

module clkDivider_10hz (

input clk,

input reset,

input i_clear,

input i_enable,

output reg o_clk

);

reg [31:0] r_counter = 0;

always@(posedge clk, posedge reset, posedge i_clear) begin

if(reset || i_clear) begin

r_counter <= 0;

o_clk <= 1'b0;

end else if(i_enable) begin

if(r_counter == 10_000_000 - 1) begin // 10hz

r_counter <= 0;

o_clk <= 1'b1;

end else begin

r_counter <= r_counter + 1;

o_clk <= 1'b0;

end

end

else r_counter <= r_counter;

end

endmodule

module upcounter (

input clk,

input reset,

input i_clear,

output reg [13:0] o_upCounter = 0

);

always@(posedge clk, posedge reset, posedge i_clear) begin

if(reset || i_clear) begin

o_upCounter <= 0;

end

else begin

if(o_upCounter == 9999) begin

o_upCounter <= 0;

end

else begin

o_upCounter <= o_upCounter + 1;

end

end

end

endmodule

adder_8bit.v

(full_adder_4bit)

`timescale 1ns / 1ps

module adder_8bit (

input [7:0] i_a,

input [7:0] i_b,

output [7:0] o_sum,

output o_carry

);

wire w_c4;

full_adder_4bit U_FA4_0 (

.i_a(i_a[3:0]),

.i_b(i_b[3:0]),

.i_cin(0),

.o_sum(o_sum[3:0]),

.o_carry(w_c4)

);

full_adder_4bit U_FA4_1 (

.i_a(i_a[7:4]),

.i_b(i_b[7:4]),

.i_cin(w_c4),

.o_sum(o_sum[7:4]),

.o_carry(o_carry)

);

endmodule

full_adder_4bit.v

(full_adder_1bit)

`timescale 1ns / 1ps

module full_adder_4bit (

input [3:0]i_a,

input [3:0]i_b,

input i_cin,

output [3:0]o_sum,

output o_carry

);

wire w_c1, w_c2, w_c3;

full_adder_1bit U_FA_0 (

.i_a(i_a[0]),

.i_b(i_b[0]),

.i_cin(i_cin),

.o_sum(o_sum[0]),

.o_carry(w_c1)

);

full_adder_1bit U_FA_1 (

.i_a(i_a[1]),

.i_b(i_b[1]),

.i_cin(w_c1),

.o_sum(o_sum[1]),

.o_carry(w_c2)

);

full_adder_1bit U_FA_2 (

.i_a(i_a[2]),

.i_b(i_b[2]),

.i_cin(w_c2),

.o_sum(o_sum[2]),

.o_carry(w_c3)

);

full_adder_1bit U_FA_3 (

.i_a(i_a[3]),

.i_b(i_b[3]),

.i_cin(w_c3),

.o_sum(o_sum[3]),

.o_carry(o_carry)

);

endmodule`timescale 1ns / 1ps

module full_adder_4bit (

input [3:0]i_a,

input [3:0]i_b,

input i_cin,

output [3:0]o_sum,

output o_carry

);

wire w_c1, w_c2, w_c3;

full_adder_1bit U_FA_0 (i_a[0], i_b[0], i_cin, o_sum[0], w_c1);

full_adder_1bit U_FA_1 (i_a[1], i_b[1], w_c1, o_sum[1], w_c2);

full_adder_1bit U_FA_2 (i_a[2], i_b[2], w_c2, o_sum[2], w_c3);

full_adder_1bit U_FA_3 (i_a[3], i_b[3], w_c3, o_sum[3], o_carry);

endmodule

full_adder_1bit.v

(half_adder)

module full_adder_1bit (

input i_a,

input i_b,

input i_cin,

output o_sum,

output o_carry

);

wire w_sum1, w_carry1, w_carry2;

half_adder U_HA_0 (

.i_a(i_a),

.i_b(i_b),

.o_sum(w_sum1),

.o_carry(w_carry1)

);

half_adder U_HA_1 (

.i_a(w_sum1),

.i_b(i_cin),

.o_sum(o_sum),

.o_carry(w_carry2)

);

assign o_carry = w_carry1 | w_carry2;

endmodulemodule full_adder_1bit (

input i_a,

input i_b,

input i_cin,

output o_sum,

output o_carry

);

wire w_sum1, w_carry1, w_carry2;

half_adder U_HA_0 (i_a, i_b, w_sum1, w_carry1);

half_adder U_HA_1 (w_sum1, i_cin, o_sum, w_carry2);

assign o_carry = w_carry1 | w_carry2;

endmodule

half_adder

module half_adder (

input i_a,

input i_b,

output o_sum,

output o_carry

);

assign o_sum = i_a ^ i_b;

assign o_carry = i_a & i_b;

endmodule

mux_2x1_14bit.v

`timescale 1ns / 1ps

module mux_2x1_14bit(

input i_sel, // i_b[7]

input [13:0] i_x0, // Calculator_Value

input [13:0] i_x1, // stopwatch_Value

output reg [13:0] o_y

);

always @(*) begin

case (i_sel)

1'b0 : o_y = i_x0;

1'b1 : o_y = i_x1;

default: o_y = 14'b0;

endcase

end

endmodule

FndController.v

(clkDivider, Counter_2bit, decoder_2x4, DigitSplitter, mux_4x1, BCDtoFND_decoder)

`timescale 1ns/1ps

module FndController (

input clk,

input reset,

input [13:0] i_sw_bcd,

output [3:0] o_digitSel,

output [7:0] o_fndFont

);

wire [1:0] w_digitSel;

wire [3:0] w_digitNumber;

wire [3:0] w_dig_1, w_dig_10, w_dig_100, w_dig_1000;

wire w_clk;

clkDivider U_clkDivider(

.i_clk(clk),

.i_reset(reset),

.o_clk(w_clk)

);

Counter_2bit U_Counter_2bit(

.clk(w_clk),

.reset(reset),

.o_count(w_digitSel)

);

decoder_2x4 U_decoder_2x4(

.i_x(w_digitSel),

.o_y(o_digitSel)

);

DigitSplitter U_DigitSplitter(

.i_number(i_sw_bcd),

.o_dig_1(w_dig_1),

.o_dig_10(w_dig_10),

.o_dig_100(w_dig_100),

.o_dig_1000(w_dig_1000)

);

mux_4x1 U_mux_4x1(

.i_sel(w_digitSel),

.i_x0(w_dig_1),

.i_x1(w_dig_10),

.i_x2(w_dig_100),

.i_x3(w_dig_1000),

.o_y(w_digitNumber)

);

BCDtoFND_decoder U_BCDtoFND_decoder(

.i_bcd(w_digitNumber),

.o_fnd(o_fndFont)

);

endmodule

clkDivider.v (100Mhz to 1Khz, Toggle)

`timescale 1ns / 1ps

module clkDivider (

input i_clk,

input i_reset,

output o_clk

);

parameter N = 50_000;

reg r_clk = 0;

reg [32:0] r_counter = 0;

assign o_clk = r_clk;

always @(posedge i_clk, posedge i_reset) begin

if(i_reset) begin

r_counter <= 0;

r_clk <= 0;

end

else begin

if(r_counter == N - 1) begin // 1kHz

r_counter <= 0;

r_clk <= ~r_clk; // high -> low, low -> high toggle

end else begin

r_counter <= r_counter+1;

end

end

end

endmodule

clkDivider.v (100Mhz to 1Khz, Comparing)

`timescale 1ns / 1ps

module clkDivider (

input clk, // 100MHz

input reset,

output reg o_clk=0 // 1KHz

);

reg [16:0] r_counter = 0;

always @(posedge clk, posedge reset) begin // Comparing, Not Toggle

if (reset) begin

r_counter <= 0;

end

else begin

if (r_counter == 100_000-1) begin

r_counter <= 0;

o_clk <= 1'b1;

end

else begin

r_counter <= r_counter + 1;

o_clk <= 1'b0;

end

end

end

endmodule

Counter_2bit.v

`timescale 1ns / 1ps

module Counter_2bit(

input clk,

input reset,

output [1:0] o_count

);

reg [1:0] r_counter = 2'b0;

assign o_count = r_counter;

always@(posedge clk, posedge reset) begin

if(reset) begin

r_counter <= 2'b0;

end

else begin

r_counter <= r_counter + 1;

end

end

endmodule

decoder_2x4.v

`timescale 1ns/1ps

module decoder_2x4(

input [1:0] i_x,

output [3:0] o_y

);

reg [3:0] o_y;

always@(i_x) begin

case(i_x)

2'b00 : o_y = 4'b0001;

2'b01 : o_y = 4'b0010;

2'b10 : o_y = 4'b0100;

2'b11 : o_y = 4'b1000;

default : o_y = 4'b0000;

endcase

end

endmodule

DigitSplitter.v

`timescale 1ns / 1ps

module DigitSplitter(

input [13:0] i_number,

output [3:0] o_dig_1,

output [3:0] o_dig_10,

output [3:0] o_dig_100,

output [3:0] o_dig_1000

);

assign o_dig_1 = i_number % 10;

assign o_dig_10 = i_number / 10 % 10;

assign o_dig_100 = i_number / 100 % 10;

assign o_dig_1000 = i_number / 1000 % 10;

endmodule

mux_4x1.v

`timescale 1ns / 1ps

module mux_4x1(

input [1:0] i_sel,

input [3:0] i_x0,

input [3:0] i_x1,

input [3:0] i_x2,

input [3:0] i_x3,

output [3:0] o_y

);

reg [3:0] o_y;

always@(*) begin

case(i_sel)

2'b00 : o_y = i_x0;

2'b01 : o_y = i_x1;

2'b10 : o_y = i_x2;

2'b11 : o_y = i_x3;

default : o_y = 4'b0;

endcase

end

endmodule

BCDtoFND_decoder.v

`timescale 1ns / 1ps

module BCDtoFND_decoder(

input [3:0] i_bcd,

output reg [7:0] o_fnd

);

always @(i_bcd) begin

case (i_bcd)

4'd0: o_fnd = 8'hc0; // 8'b11000000; // 0

4'd1: o_fnd = 8'hf9;

4'd2: o_fnd = 8'ha4;

4'd3: o_fnd = 8'hb0;

4'd4: o_fnd = 8'h99;

4'd5: o_fnd = 8'h92;

4'd6: o_fnd = 8'h82;

4'd7: o_fnd = 8'hf8;

4'd8: o_fnd = 8'h80;

4'd9: o_fnd = 8'h90;

default: o_fnd = 8'hff;

endcase

end

endmodule

My_Basys-3-Master.xdc

(Clock signal, Switches)

## Clock signal

set_property -dict { PACKAGE_PIN W5 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #IO_L12P_T1_MRCC_34 ,Sch=CLK100MHZ

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

##Switches

set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports { i_a[0] }]; #IO_L19N_T3_A09_D25_VREF_14 ,Sch=SW0

set_property -dict { PACKAGE_PIN V16 IOSTANDARD LVCMOS33 } [get_ports { i_a[1] }]; #IO_L19P_T3_A10_D26_14 ,Sch=SW1

set_property -dict { PACKAGE_PIN W16 IOSTANDARD LVCMOS33 } [get_ports { i_a[2] }]; #IO_L20P_T3_A08_D24_14 ,Sch=SW2

set_property -dict { PACKAGE_PIN W17 IOSTANDARD LVCMOS33 } [get_ports { i_a[3] }]; #IO_L20N_T3_A07_D23_14 ,Sch=SW3

set_property -dict { PACKAGE_PIN W15 IOSTANDARD LVCMOS33 } [get_ports { i_a[4] }]; #IO_L21N_T3_DQS_A06_D22_14 ,Sch=SW4

set_property -dict { PACKAGE_PIN V15 IOSTANDARD LVCMOS33 } [get_ports { i_a[5] }]; #IO_L21P_T3_DQS_14 ,Sch=SW5

set_property -dict { PACKAGE_PIN W14 IOSTANDARD LVCMOS33 } [get_ports { i_a[6] }]; #IO_L22N_T3_A04_D20_14 ,Sch=SW6

set_property -dict { PACKAGE_PIN W13 IOSTANDARD LVCMOS33 } [get_ports { i_a[7] }]; #IO_L22P_T3_A05_D21_14 ,Sch=SW7

set_property -dict { PACKAGE_PIN V2 IOSTANDARD LVCMOS33 } [get_ports { i_b[0] }]; #IO_L5P_T0_34 ,Sch=SW8

set_property -dict { PACKAGE_PIN T3 IOSTANDARD LVCMOS33 } [get_ports { i_b[1] }]; #IO_L2N_T0_34 ,Sch=SW9

set_property -dict { PACKAGE_PIN T2 IOSTANDARD LVCMOS33 } [get_ports { i_b[2] }]; #IO_L1N_T0_34 ,Sch=SW10

set_property -dict { PACKAGE_PIN R3 IOSTANDARD LVCMOS33 } [get_ports { i_b[3] }]; #IO_L2P_T0_34 ,Sch=SW11

set_property -dict { PACKAGE_PIN W2 IOSTANDARD LVCMOS33 } [get_ports { i_b[4] }]; #IO_L5N_T0_34 ,Sch=SW12

set_property -dict { PACKAGE_PIN U1 IOSTANDARD LVCMOS33 } [get_ports { i_b[5] }]; #IO_L3N_T0_DQS_34 ,Sch=SW13

set_property -dict { PACKAGE_PIN T1 IOSTANDARD LVCMOS33 } [get_ports { i_b[6] }]; #IO_L3P_T0_DQS_34 ,Sch=SW14

set_property -dict { PACKAGE_PIN R2 IOSTANDARD LVCMOS33 } [get_ports { i_b[7] }]; #IO_L1P_T0_34 ,Sch=SW15

My_Basys-3-Master.xdc

(7 segment display, Buttons)

##7 segment display

set_property -dict { PACKAGE_PIN W7 IOSTANDARD LVCMOS33 } [get_ports { o_fndFont[0] }]; #IO_L13P_T2_MRCC_34 ,Sch=CA

set_property -dict { PACKAGE_PIN W6 IOSTANDARD LVCMOS33 } [get_ports { o_fndFont[1] }]; #IO_L13N_T2_MRCC_34 ,Sch=CB

set_property -dict { PACKAGE_PIN U8 IOSTANDARD LVCMOS33 } [get_ports { o_fndFont[2] }]; #IO_L14P_T2_SRCC_34 ,Sch=CC

set_property -dict { PACKAGE_PIN V8 IOSTANDARD LVCMOS33 } [get_ports { o_fndFont[3] }]; #IO_L14N_T2_SRCC_34 ,Sch=CD

set_property -dict { PACKAGE_PIN U5 IOSTANDARD LVCMOS33 } [get_ports { o_fndFont[4] }]; #IO_L16P_T2_34 ,Sch=CE

set_property -dict { PACKAGE_PIN V5 IOSTANDARD LVCMOS33 } [get_ports { o_fndFont[5] }]; #IO_L16N_T2_34 ,Sch=CF

set_property -dict { PACKAGE_PIN U7 IOSTANDARD LVCMOS33 } [get_ports { o_fndFont[6] }]; #IO_L19P_T3_34 ,Sch=CG

set_property -dict { PACKAGE_PIN V7 IOSTANDARD LVCMOS33 } [get_ports { o_fndFont[7] }]; #IO_L19N_T3_VREF_34 ,Sch=DP

set_property -dict { PACKAGE_PIN U2 IOSTANDARD LVCMOS33 } [get_ports { o_digitSel[0] }]; #IO_L9N_T1_DQS_34 ,Sch=DP

set_property -dict { PACKAGE_PIN U4 IOSTANDARD LVCMOS33 } [get_ports { o_digitSel[1] }]; #IO_L11P_T1_SRCC_34 ,Sch=DP

set_property -dict { PACKAGE_PIN V4 IOSTANDARD LVCMOS33 } [get_ports { o_digitSel[2] }]; #IO_L11N_T1_SRCC_34 ,Sch=DP

set_property -dict { PACKAGE_PIN W4 IOSTANDARD LVCMOS33 } [get_ports { o_digitSel[3] }]; #IO_L12N_T1_MRCC_34 ,Sch=DP

##Buttons

set_property -dict { PACKAGE_PIN U18 IOSTANDARD LVCMOS33 } [get_ports { reset }]; #IO_L18N_T2_A11_D27_14 ,Sch=BTNC

set_property -dict { PACKAGE_PIN T18 IOSTANDARD LVCMOS33 } [get_ports { i_pbstoprun }]; #IO_L17N_T2_A13_D29_14 ,Sch=BTNU

#set_property -dict { PACKAGE_PIN W19 IOSTANDARD LVCMOS33 } [get_ports { btnL }]; #IO_L16N_T2_A15_D31_14 ,Sch=BTNL

#set_property -dict { PACKAGE_PIN T17 IOSTANDARD LVCMOS33 } [get_ports { btnR }]; #IO_L17P_T2_A14_D30_14 ,Sch=BTNR

set_property -dict { PACKAGE_PIN U17 IOSTANDARD LVCMOS33 } [get_ports { i_pbclear }]; #IO_L18P_T2_A12_D28_14 ,Sch=BTND

Schematic

'[Harman] 반도체 설계 > Vivado' 카테고리의 다른 글

| [Vivado] 07. Calculator 8bit, PB FSM StopWatch (0) | 2023.08.05 |

|---|---|

| [Vivado] 06. Calculator 8bit, FSM StopWatch 0.1s UpCount (0) | 2023.08.05 |

| [Vivado] 05. Finite State Machine LED (0) | 2023.08.05 |

| [Vivado] 04. FndController, Adder 8bit (0) | 2023.08.05 |

| [Vivado] 03. Adder 8bit (0) | 2023.08.05 |